dheerajc

Newbie level 4

Hello all,

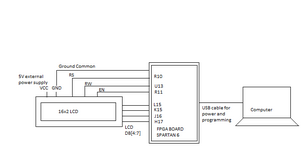

I have written a code in verilog for interfacing of 16x2 LCD with Numato Uno Spartan 6 FPGA board. Clock is 100 Mhz. However LCD is not even getting initialized. Can someone please tell me what is wrong with the logic.

And this is the constraint file.

I have written a code in verilog for interfacing of 16x2 LCD with Numato Uno Spartan 6 FPGA board. Clock is 100 Mhz. However LCD is not even getting initialized. Can someone please tell me what is wrong with the logic.

Code:

module my_lcd(

input clk,

output reg rs,en,rw,

output reg [7:4] LCD_out

);

reg[7:0] count=0;

reg [24:0] i=0;

reg [7:0] char_data;

reg [7:0] j;

reg [24:0] num =0;

reg [3:0] lcd_data;

initial begin

/* LCD Power ON Initialization time >15ms */

rs=0;

en=0;

rw=0;

Delay(2000000); //20 ms delay

end

always@(posedge clk)begin

//if(count==10)count=0;

case(count)

0 : begin

LCD_Command (8'h28); /* Initialization of 16X2 LCD in 4bit mode */

// char_data = (8'h0F & 8'h28);

// LCD_out = /*(LCD_out & 8'h0F) |*/ (char_data << 4);

count <= count + 1'b1;

end

1 : begin

LCD_Command (8'h01); //clear display screen

//char_data = (8'h0F & 8'h01);

//LCD_out = (char_data << 4);

count <= count + 1'b1;

end

2 : begin

LCD_Command (8'h02); //Return home

//char_data = (8'h0F & 8'h02);

//LCD_out = (char_data << 4);

count <= count + 1'b1;

end

3 : begin

LCD_Command (8'h0E); //Display ON cursor blinking

//char_data = (8'h0F & 8'h0E);

//LCD_out = (char_data << 4);

count <= count + 1'b1;

end

4 : begin

LCD_Command (8'h0F); //Display ON cursor blinking

//char_data = (8'h0F & 8'h0E);

//LCD_out = (char_data << 4);

count <= count + 1'b1;

end

5 : begin

LCD_Data(8'h48); //'H'

//char_data = (8'h0F & 8'h0F);

//LCD_out = (char_data << 4);

count <= count + 1'b1;

end

6 : begin

LCD_Command (8'h14); //Display ON cursor blinking

//char_data = (8'h0F & 8'h0E);

//LCD_out = (char_data << 4);

count <= count + 1'b1;

end

7 : begin

LCD_Data(8'h45); //'E'

//char_data = (8'h0F & 8'h0F);

//LCD_out = (char_data << 4);

count <= count + 1'b1;

end

8 : begin

LCD_Command (8'h14); //Display ON cursor blinking

//char_data = (8'h0F & 8'h0E);

//LCD_out = (char_data << 4);

count <= count + 1'b1;

end

9 : begin

LCD_Data(8'h4C); //'L'

//char_data = (8'h0F & 8'h0F);

//LCD_out = (char_data << 4);

count <= count + 1'b1;

end

10 : begin

LCD_Command (8'h14); //Display ON cursor blinking

//char_data = (8'h0F & 8'h0E);

//LCD_out = (char_data << 4);

count <= count + 1'b1;

end

11 : begin

LCD_Data(8'h4C); //'L'

//char_data = (8'h0F & 8'h0F);

//LCD_out = (char_data << 4);

count <= count + 1'b1;

end

12 : begin

LCD_Command (8'h14); //Display ON cursor blinking

//char_data = (8'h0F & 8'h0E);

//LCD_out = (char_data << 4);

count <= count + 1'b1;

end

13 : begin

LCD_Data(8'h4C); //'L'

//char_data = (8'h0F & 8'h0F);

//LCD_out = (char_data << 4);

count <= count + 1'b1;

end

14 : begin

LCD_Command (8'h14); //Display ON cursor blinking

//char_data = (8'h0F & 8'h0E);

//LCD_out = (char_data << 4);

count <= count + 1'b1;

end

15 : begin

LCD_Data(8'h4F); //'O'

//char_data = (8'h0F & 8'h0F);

//LCD_out = (char_data << 4);

count <= count + 1'b1;

end

16 : begin

LCD_Command (8'h14); //Display ON cursor blinking

//char_data = (8'h0F & 8'h0E);

//LCD_out = (char_data << 4);

count <= 1'b1;

end

default : LCD_Data(8'h48); //By default display 'H'

endcase

end

////

task LCD_Command (input [7:0] j);

begin

rs=0; /* Command reg. */

Delay(100000); //1 ms delay

rw=0;

Delay(100000);

//LCD_out = (LCD_out & 8'h0F) |(j & 8'h0F);//(LCD_out & 8'h0F) |(j & 8'hF0);/* Send upper nibble */

LCD_out = ( j & 8'hF0);

/* Write operation */

en=1;

Delay(500000);

en=0;

Delay(500000);

LCD_out = /*(LCD_out & 8'h0F) |*/ (8'hF0)&(j << 4);/* Send lower nibble */

en=1; /* Enable pulse */

Delay(500000);

en=0;

Delay(500000);

end

endtask

//

task LCD_Data (input [7:0] char_data);

begin

rs=1; /*Data reg.*/

Delay(100000);

rw=0; /*Write operation*/

Delay(100000);

//LCD_out = (LCD_out & 8'h0F) | (char_data & 8'h0F);//(LCD_out & 8'h0F) | (char_data & 8'hF0);/* Send upper nibble */

LCD_out = ( char_data & 8'hF0);

en=1'b1;

Delay(500000); //5 ms delay

en=1'b0;

Delay(500000); //5 ms delay

LCD_out = /*(LCD_out & 8'h0F) |*/ (8'hF0)&(char_data << 4);/* Send lower nibble */

en=1'b1; /* Enable pulse */

Delay(500000); //5 ms delay

en=1'b0;

Delay(500000); //5 ms delay

end

endtask

task Delay (input [24:0] i);

begin

if(num == i) num =0;

else num = num + 1;

end

endtask

endmoduleAnd this is the constraint file.

Code:

NET "clk" LOC = V10; //100 Mhz clock

NET "rs" LOC = R10 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST ; #Pin 3 //P8

NET "en" LOC = R11 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST ; #Pin 1 //P8

NET "rw" LOC = U13 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST ; #Pin 5 //P8

//NET "LCD_out[0]" LOC = H17 ; //| IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST ; #Pin 1 //P9

//NET "LCD_out[1]" LOC = J16 ; //| IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST ; #Pin 3 //P9

//NET "LCD_out[2]" LOC = K15 ; //| IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST ; #Pin 5 //P9

//NET "LCD_out[3]" LOC = L15 ; //| IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST ; #Pin 7 //P9

NET "LCD_out[4]" LOC = L15 ; //| IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST ; #Pin 1 //P9

NET "LCD_out[5]" LOC = K15 ; //| IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST ; #Pin 3 //P9

NET "LCD_out[6]" LOC = J16 ; //| IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST ; #Pin 5 //P9

NET "LCD_out[7]" LOC = H17 ; //| IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST ; #Pin 7 //P9