melkord

Full Member level 3

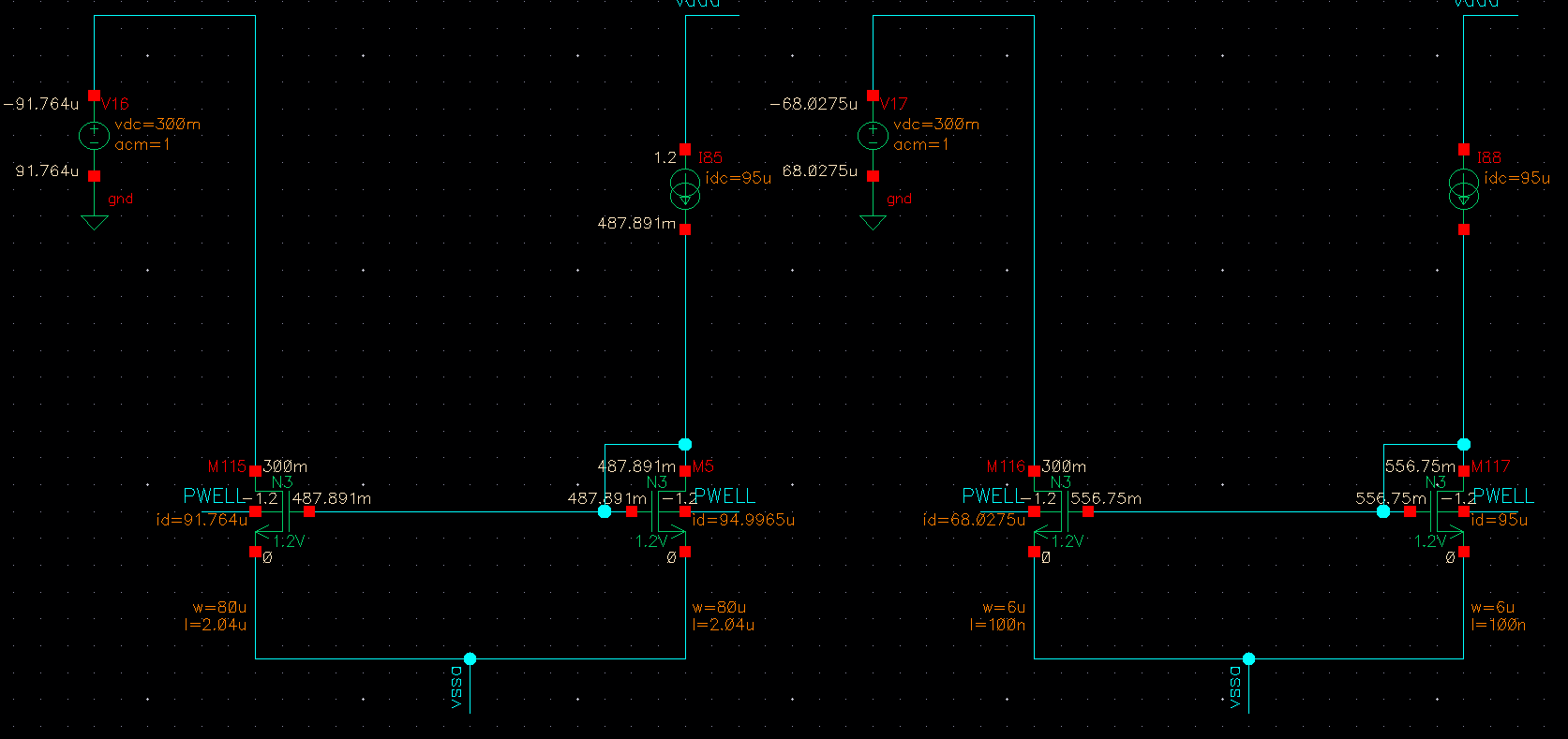

I am designing a stage source follower with bias current around 90uA.

It seems that I need large size, W and L, to get good accuracy.

Basic formula teaches us that increasing W leads to more id but somehow it does not work here.

What effect explains this? Am I missing something?

Here is a comparison with smaller current mirror which cannot give me anything near 90uA.

It seems that I need large size, W and L, to get good accuracy.

Basic formula teaches us that increasing W leads to more id but somehow it does not work here.

What effect explains this? Am I missing something?

Here is a comparison with smaller current mirror which cannot give me anything near 90uA.