canarybird33

Member level 1

- Joined

- Apr 16, 2013

- Messages

- 41

- Helped

- 2

- Reputation

- 4

- Reaction score

- 2

- Trophy points

- 1,288

- Location

- Mashhad, Iran, Iran

- Activity points

- 1,591

Hello all,

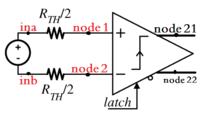

In my searches,the below method is used to calculate kickback noise.(Rth=8kohm; according to the this paper "Kickback Noise Reduction Techniques for CMOS Latched Comparators"]

My simulation doesn't show sensible results. I mean, when I apply this method, the comparator does not work properly. the simulatin results are as follows (Node 21 and Node 22 are outputs):

My questions are:

should the comparator work as normal when calculating kickback noise?

Is the Rth=8kohm a general rule? Why 8k?

How should I apply the ina and inb as inputs?(I have applied 2 separate pulse to create the signal as same as the paper I mentioned above)

Thanks.

In my searches,the below method is used to calculate kickback noise.(Rth=8kohm; according to the this paper "Kickback Noise Reduction Techniques for CMOS Latched Comparators"]

My simulation doesn't show sensible results. I mean, when I apply this method, the comparator does not work properly. the simulatin results are as follows (Node 21 and Node 22 are outputs):

My questions are:

should the comparator work as normal when calculating kickback noise?

Is the Rth=8kohm a general rule? Why 8k?

How should I apply the ina and inb as inputs?(I have applied 2 separate pulse to create the signal as same as the paper I mentioned above)

Thanks.

Last edited: