anotherbrick

Full Member level 4

- Joined

- Jan 10, 2009

- Messages

- 217

- Helped

- 1

- Reputation

- 2

- Reaction score

- 1

- Trophy points

- 1,298

- Location

- Istanbul , Turkey

- Activity points

- 3,143

hello dear forum

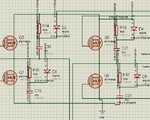

I want to add snubber to my mosfet H bridge

the DC link voltage is 300 VDC

and the H bridge circuit works as inverter producing 30 - 100 Hz alternating square wave

the values of components is not true I will use 100 nF and 1 K and UF4007

I want to ask if the following scheme is correct ?

thank you

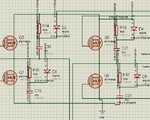

I want to add snubber to my mosfet H bridge

the DC link voltage is 300 VDC

and the H bridge circuit works as inverter producing 30 - 100 Hz alternating square wave

the values of components is not true I will use 100 nF and 1 K and UF4007

I want to ask if the following scheme is correct ?

thank you