janlee

Newbie level 5

pci9054

In my project I use PCI9054 "C Mode" to control FPGA and other peripherals.Acturally PCI9054 acts as local bus master and PCI target.

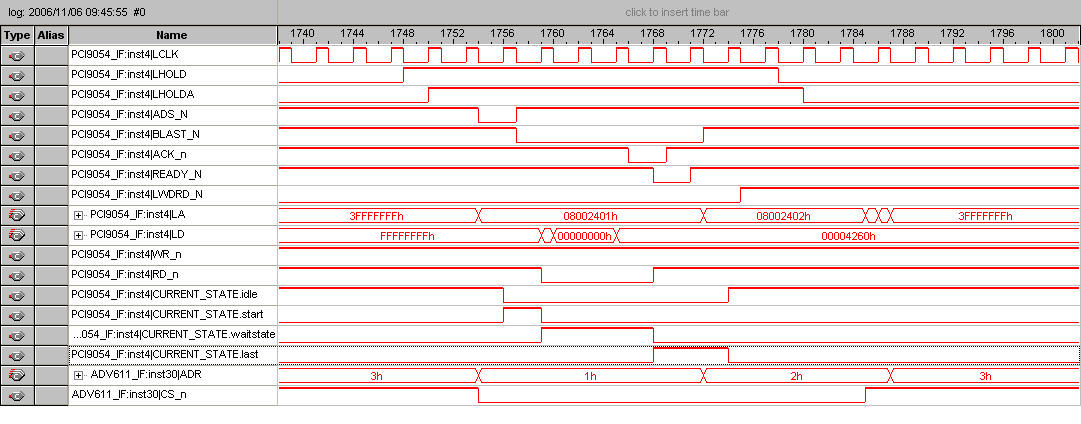

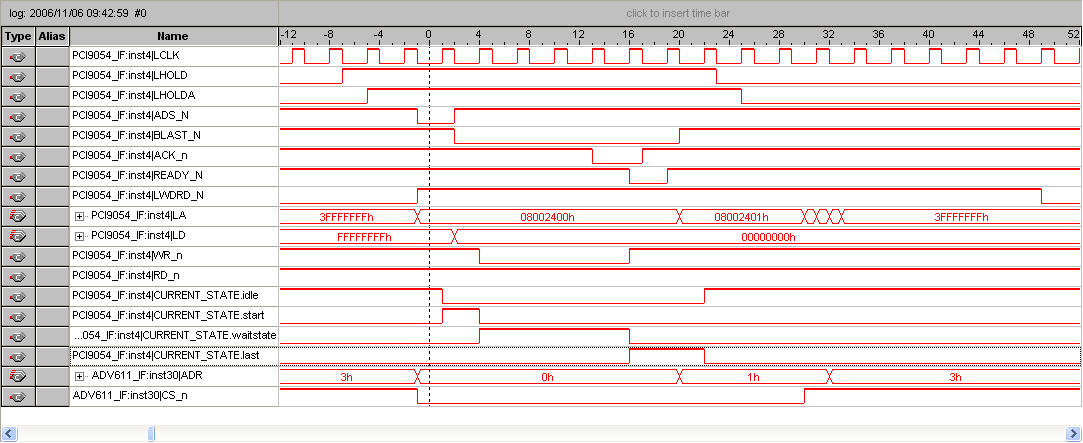

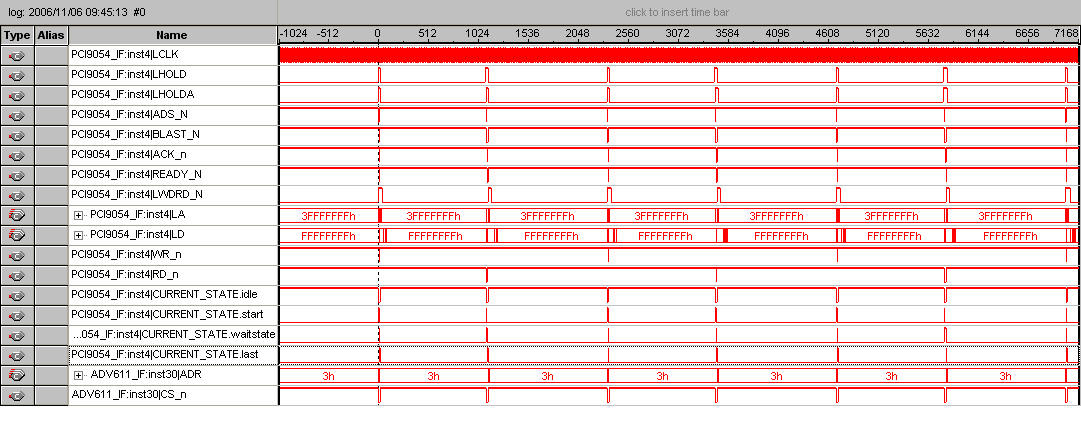

I successfully realize the signal cycle 32 bits read & write.But it quite slow,the interval between two continous read or write is more than 12 us.To control register in the FPGA is not a problem,but to transfer large block of data in real time it is not accecptable.

Now my question is how to configure the PCI9054 to lanch a burst transfer via PLX's funcions(I wonder which function I can use) ,and how to modify my code to adapt this transfer.

Many appreciations.

In my project I use PCI9054 "C Mode" to control FPGA and other peripherals.Acturally PCI9054 acts as local bus master and PCI target.

I successfully realize the signal cycle 32 bits read & write.But it quite slow,the interval between two continous read or write is more than 12 us.To control register in the FPGA is not a problem,but to transfer large block of data in real time it is not accecptable.

Now my question is how to configure the PCI9054 to lanch a burst transfer via PLX's funcions(I wonder which function I can use) ,and how to modify my code to adapt this transfer.

Many appreciations.

Code:

---------------------------------------------

--Module : PCI9054 interface Module

--File : PCI9054_IF.vhd

--Library : IEEE;

--Description : PCI9054 interface controller

--Simulator : Modelsim 5.8/WindowsXP

--Synthesizer :

--Author :

--Created : 06/07/2006

--Last update : 25/07/2006

---------------------------------------------

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity PCI9054_IF is

port(

RST_N : in std_logic;

LCLK : in std_logic;

LHOLD : in std_logic;

ADS_N : in std_logic;

BLAST_N : in std_logic;

LWDRD_N : in std_logic;

LA : in std_logic_vector(31 downto 2);

LD : inout std_logic_vector(31 downto 0);

LHOLDA : out std_logic;

READY_N : out std_logic;

ACK_n : in std_logic;

WR_n : out std_logic;

RD_n : out std_logic

);

end PCI9054_IF;

architecture RTL of PCI9054_IF is

type STATE_TYPE is (IDLE,START,WAITSTATE,LAST);

signal CURRENT_STATE,NEXT_STATE : STATE_TYPE;

signal iready_n : std_logic;

signal iwr_n,ird_n : std_logic;

signal iaddr : std_logic_vector(31 downto 2);

begin

--

--Grant for local bus request

process(LCLK)

begin

if (LCLK'event and LCLK = '1') then

if LHOLD = '1' then

LHOLDA <= LHOLD;

else

LHOLDA <= '0';

end if;

end if;

end process;

--State Machine Transition

process(LCLK)

begin

if RST_n = '0' then

CURRENT_STATE <= IDLE;

elsif(LCLK'event and LCLK = '1') then

CURRENT_STATE <= NEXT_STATE;

if CURRENT_STATE = IDLE and ADS_N = '0'then

iaddr <= LA;

end if;

READY_n <= iready_n ;

end if;

end process;

--State Machine

process(CURRENT_STATE,ADS_N,LWDRD_N,BLAST_N,ACK_n)

begin

NEXT_STATE <= CURRENT_STATE;

case CURRENT_STATE is

when IDLE =>

RD_n <= '1';

WR_n <= '1';

iready_n <= '1';

if ADS_N = '0' then

NEXT_STATE <= START;

else

NEXT_STATE <= IDLE;

end if;

when START =>

RD_n <= '1';

WR_n <= '1';

iready_n <= '1';

if BLAST_N = '0' then

NEXT_STATE <= WAITSTATE;

else

NEXT_STATE <= START;

end if;

when WAITSTATE =>

RD_n <= LWDRD_N;

WR_n <= not LWDRD_N;

if iaddr(31 downto 4) = B"0010_0000_0000_0000_1001_0000_0000" then

if ACK_n = '0' then

NEXT_STATE <= LAST;

iready_n <= '0';

else

NEXT_STATE <= WAITSTATE;

iready_n <= '1';

end if;

else

NEXT_STATE <= LAST;

iready_n <= '0';

end if;

when LAST =>

RD_n <= '1';

WR_n <= '1';

iready_n <= '1';

if ADS_N = '1' and BLAST_N = '1' then

NEXT_STATE <= IDLE;

elsif ADS_N = '0' then

NEXT_STATE <= START;

else

NEXT_STATE <= LAST;

end if;

when others =>

RD_n <= '1';

WR_n <= '1';

iready_n <= '1';

NEXT_STATE <= IDLE;

end case;

end process;

end RTL;