orienteraren

Junior Member level 1

Hi!

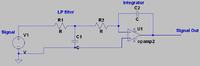

I have a low voltage signal (range +/- 50 mV) after I run it through a simple LP filter. I now want to integrate the signal using a larger capacitor but if I connect the signal to the - input on the OP amp I get 0V, both on the input and on the output. I suppose this is a fundamental think in my design, any suggestions?

Best Regards

Fredrik

I have a low voltage signal (range +/- 50 mV) after I run it through a simple LP filter. I now want to integrate the signal using a larger capacitor but if I connect the signal to the - input on the OP amp I get 0V, both on the input and on the output. I suppose this is a fundamental think in my design, any suggestions?

Best Regards

Fredrik