Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

Hi,

I'd say it's no suitable SMPS design.

It may work or not.

I doubt it can work reliably.

I doubt it can fulfill EMI/EMC requirements.

I doubt it fulfills all the creepage distance and clearance requirements.

I recommend to

* read through the datasheets, especially the chapters "PCB layout considerations" and "design considerations"

* read through application notes, that every semiconductor manufacturer provides.... for free

* go through reference desings

* read through threads here in the forum

I wonder why you used no GND plane. (No, a copper pour is no GND plane). There is plenty of free board space. And it takes less than just a couple of minutes to draw a GND polygon (without other traces, without cuts)...and add some vias.

Klaus

Read through some threads here.could you elaborate on a ground plane? i made the top layer gnd for the non isolated and isolated side.

Hi,

Read through some threads here.

I already had replied with lenghty explanations several times.

I'm sure you will find them with a forum search..

Again: you used copper pour ... it is cut in pieces

Maybe this helps:

Imagine an area of 5m x 5m of thick plastic foam on a lake. It's easy to walk on it.

Now cut the foam area in pieces of random size .... and try to walk on it.

Klaus

Some additional remarks.

1. KlausST commented already about the fragmented copper pour. I notice that you have placed jumper traces to connect the HV ground isles. Why not almost flooding the bottom side and placing many redundant bridge vias? Although the created ground can't compete with a true ground plane on a multilayer board, it may suffice for this design.

2. I see insufficient clearance and creepage in many places, e.g. 0.4 mm between HV DC and PE at the heat sink mount, also < 2 mm between HV and isolated 5V below the 5V DC/DC.

3. I expect problems in the "wide spread" gate driver traces. Low side gate nets and return have huge return loop.

4. You have zero DC bus bypass capacitors except for the bulk electrolyte capacitors, separated by a probably inductive current shunt.

Hi,

Much better now.

I didn't check clearance and creepage distances.

The red GND areas are useless, at least the very very most of them.

Keep them, if you like them.

But reduce the traces in the blue layer.

I miss thermals at the smd pads.

It's hard to detect details. Maybe increase picture resolution next time.

Use a lossless picture format like .png.

Currently I'm working on my tablet. In half a day I'm on my PC and could show some improvements.

Klaus

No! Functional isolation is just within one voltage net.regarding creepage and clerance, i just need functional i guess, because the interface is isolated.

No. Thermals on the SMD pads that are connected to the copper pour. I can´t recognize them.do you mean thermal vias?

Hi,

No! Functional isolation is just within one voltage net.

Especially where you have galvanically isolated parts you need at least "basic isolation".

It depends on a lot of things. Your countrie´s regulations, voltages, dirt, altitude, protection level....

You urgently need through some (boring and often hard to understand) regulations.

There are more or less reliable documents in the internet and even video tutorials.

****

Example:

Even if an optocoupler is rated for 4000V/1min it does not mean that it is legal to use it on an 230V AC application.

For many 230V AC applications you should go for 7mm (at least 6mm) of creepage distance.

Many optocouplers can not satisfy this.

Maybe your optocouper is suitable, I´m not sure.... but your DCDC converter most probaly is not according safety regulations.

Again: it depends on a lot of parameters.

AND:

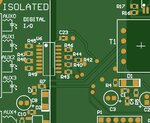

hard corners (at areas) are a NO GO. They increase electric field strength and thus functionallly reduce creepage distance.

You need to use arcs.

No. Thermals on the SMD pads that are connected to the copper pour. I can´t recognize them.

*****

Layout:

Put Q7 close to the relay, thus you shorten the traces that carry the relay current. And you don´t need that wide trace.

Feed the control trace on the red layer as much as possible. Maybe use several short pieces. Don´t cut the GND plane on the blue layer.

(My recommendation: from pad to the inner of the IC, then in direction of U5 as much as possible.)

Maybe R24 goes to an ADC. Then put R24 (not R23...) close to the ADC. This increases the precision because it better relates to ADC_GND. Consider to use a capacitor in parallel to R24.

Feed the trace from R23 to R24 on the red layer as much as possible. Maybe use several short pieces. Don´t cut the GND plane on the blue layer.

R12, R22, R23 ... I think they need more clearance around...

The supply trace to R25/LED3 could be easily shortened on the blue layer ... by moving the via in direction of pin10 of U1.

Be sure R26 is a low impedance one. No wirewound.

The traces to the power transistors are rather narraw. I don´t know your schematic ... but usually they carry fast high peak current signals... and they need a suitable feedback path.

Mind: There is no signal "from A to B" always has to be the feedback path from B to A. And it needs to be routed as carefully as the way from A to B. Best if it runs exacly the way from A to B on the opposite layer. Otherwise you get high series inductance causing ringing (worst case: self destructive), high EMI and maybe low efficiency.

There may be more issues.

Klaus

No need to get even wider.The traces from the gate resistors i thickened from 0.5mm to 1mm.

Cant seem to get much thicker before the gate resistor, opinion?

You ask.. So I repeat my opinion: The top GND is useless. You might add vias as you like, but it won´t be any significant electrical improvement.Vias. should i add more? i exposed copper so i can use some of em as testpoints.

Hi,

No need to get even wider.

on the first pictures they rather looked like 0.15mm than 0.5mm.

The resistance with 1mm is not the problem now. Now it´s the inductance causing high impedance... you now can´t lower the impedance (significantly) by increasing the width or thickness. Even 10mm won´t be much of a benefit.

It now more depends on the missing return path.

You ask.. So I repeat my opinion: The top GND is useless. You might add vias as you like, but it won´t be any significant electrical improvement.

If there will be a spark from230V area to isolated area, then I predict it will be close to C16 because of the sharp edge opposite to 16.

Mind to use standoffs at the heatsink. Solderstop is no isolation according safety regulations.

I assume it will work.

But the same time I assume it is not according safety regulations and EMI/EMC regulations.

Use a fire proof mat. Not that I think it will immediately cause fire, but in case there is some little conductive dirt..and it causes a spark ... there is a good chance that it won´t slef extinguish because of low functional isolation.

This is especially true for the 325V DC bus.

Use it on your own risk, don´t let anybody else touch it. Nothing.

Let us know how it behaves...

Klaus

I'm saying useless, because 99% of the area is free of current. And I think it's good the way it is.why im confused about top gnd and vias is two fold, one is caught someone saying use many as many vias as you want in your design, more is better to a degree.

Heatsinks are made from conductive metal. You connected them to Earth ground. So you need to electrically isolate them from top layer signals. Plastic standoffs maybe could help.Im sorry if i quite dont understand, but could you link something about heatsink standoffs?

Hi,

Again: you used copper pour ... it is cut in pieces

Maybe this helps:

Imagine an area of 5m x 5m of thick plastic foam on a lake. It's easy to walk on it.

Now cut the foam area in pieces of random size .... and try to walk on it.

Klaus

Don't agree. IEC 61010 and similar standards for specific application ranges are in force almost worldwide. Mains voltage <300 V, overvoltage category II, pollution degree 2 requires 1.5 mm PCB clearance and creepage for basic insulation, doubled value for reinforced insulation.I know the regulations for safety are different in each country, they are hard to read and hard to understand...and often expensive.