Debdut

Full Member level 3

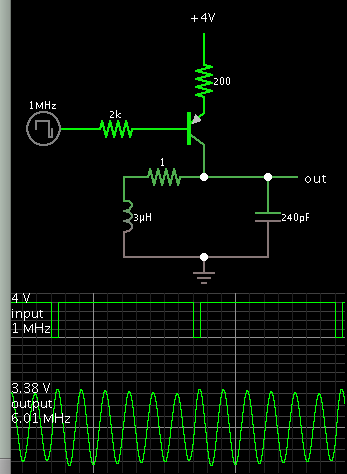

I have a rectangular voltage wave of frequency 1 MHz. I need to frequency multiply it to 6 MHz. Is it possible by injection locking?

If any other method for frequency multiplication is possible, please mention.

I thought of creating a PLL, but the control voltage of the PLL has fluctuations in time domain. So the 6 MHz output I would get through the PLL will not have exactly, 166.666ns period throughout!

If any other method for frequency multiplication is possible, please mention.

I thought of creating a PLL, but the control voltage of the PLL has fluctuations in time domain. So the 6 MHz output I would get through the PLL will not have exactly, 166.666ns period throughout!