jkbagada

Newbie level 6

Hello friends

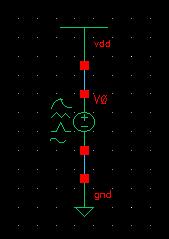

I have imported a synthesized Verilog netlist to Cadence for spice simulations. Now i see there are no VCC, GND pins at top level. while down at standard cell level VCC, GND pins can be seen. I tried running simulations by giving stimuli in ADE at Global sources but shows errors, moreover i dont wish to give supply by stimuli.

How do i give supply (by connecting voltage source) at the top most hierarchy?

Thank you!

I have imported a synthesized Verilog netlist to Cadence for spice simulations. Now i see there are no VCC, GND pins at top level. while down at standard cell level VCC, GND pins can be seen. I tried running simulations by giving stimuli in ADE at Global sources but shows errors, moreover i dont wish to give supply by stimuli.

How do i give supply (by connecting voltage source) at the top most hierarchy?

Thank you!