Junus2012

Advanced Member level 5

Hello,

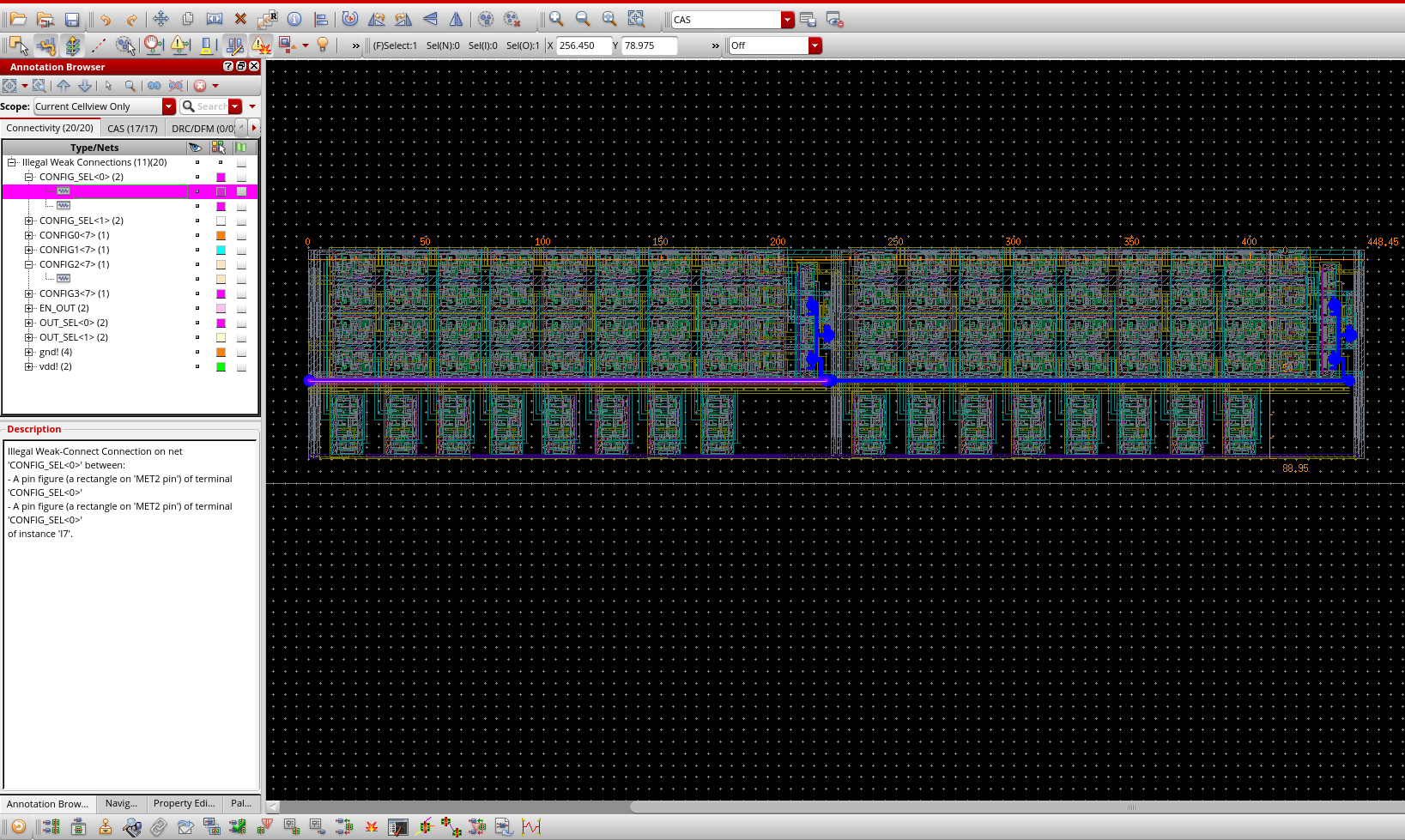

I am designing serial shift register, I have noticed after the 16 bit length the Cadence "Check against Source" in Layout GXL tool give me connectivity warning about illegal week connection.

However my design passed successfully the DRC and the LVS and the post layout simulation is running perfectly.

But I am not sure if this warning is harmful or I can live with it

Please see the attached image, I have traced one of the weak connection

Best Regards

I am designing serial shift register, I have noticed after the 16 bit length the Cadence "Check against Source" in Layout GXL tool give me connectivity warning about illegal week connection.

However my design passed successfully the DRC and the LVS and the post layout simulation is running perfectly.

But I am not sure if this warning is harmful or I can live with it

Please see the attached image, I have traced one of the weak connection

Best Regards