Ata_sa16

Full Member level 6

- Joined

- Mar 29, 2016

- Messages

- 343

- Helped

- 59

- Reputation

- 118

- Reaction score

- 58

- Trophy points

- 28

- Location

- Milky Way Galaxy, 179° 56′ 39.4″

- Activity points

- 2,221

Hi all,

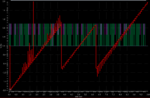

I am trying to simulate 1.5 bit ADC stage (switched capacitor topology).

I used ideal components. I am getting the correct plot; however, I have voltage spikes at the output (Kv level).

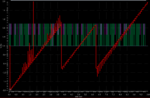

I tried to add parasitic capacitance to make switches little bit realistic but it does not work.

I am attaching all plots. Thank you for your time and effort.

I figured out that my switch turns on when v=1 so something happens between 0-1. I fixed the problem with lowering switch threshold to 0.5

This does not let vout rise during clock transition. I am trying to find out why this happens ...

ideal switch

After making threshold vclose = 0.5

I am trying to simulate 1.5 bit ADC stage (switched capacitor topology).

I used ideal components. I am getting the correct plot; however, I have voltage spikes at the output (Kv level).

I tried to add parasitic capacitance to make switches little bit realistic but it does not work.

I am attaching all plots. Thank you for your time and effort.

I figured out that my switch turns on when v=1 so something happens between 0-1. I fixed the problem with lowering switch threshold to 0.5

This does not let vout rise during clock transition. I am trying to find out why this happens ...

ideal switch

After making threshold vclose = 0.5

Last edited: