Xenon02

Full Member level 3

Hello !

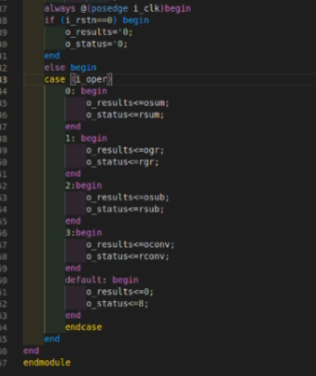

I do have a problem understanding this code :

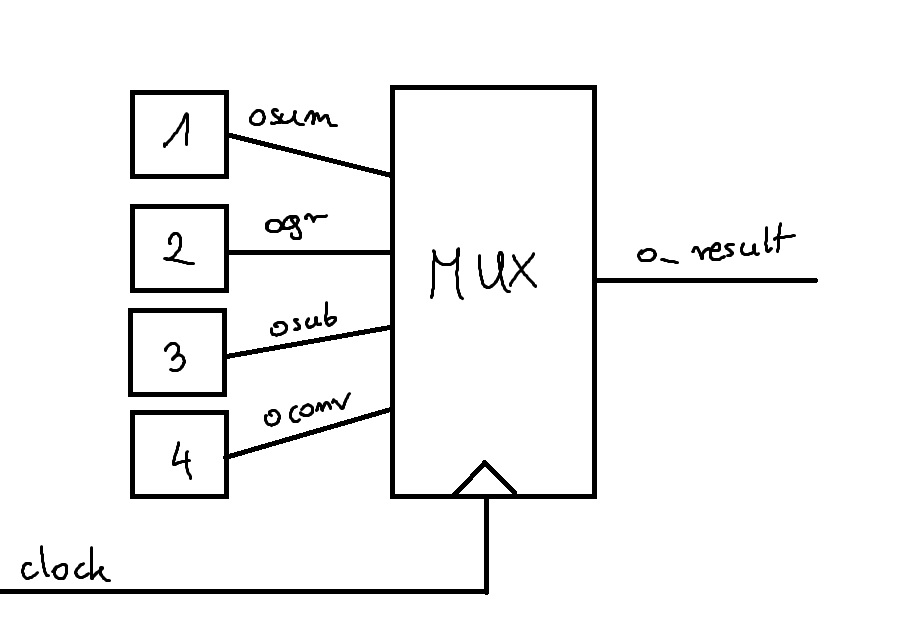

It looks like as if the multiplexer (which is this "case" here) is something like synchronized mux like here:

Something like that exist ? I couldn't find something like that on the website.

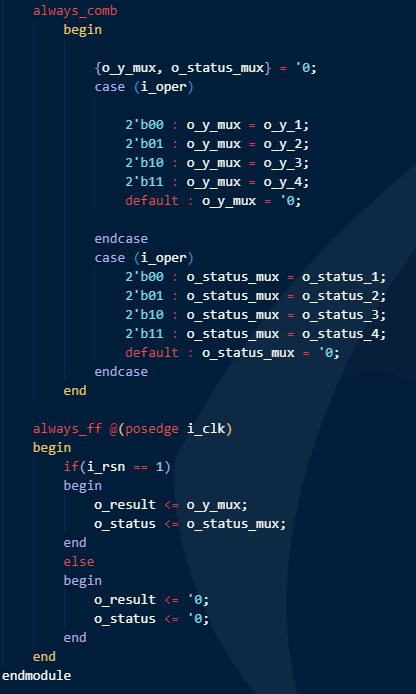

But my code looks a bit different more logical

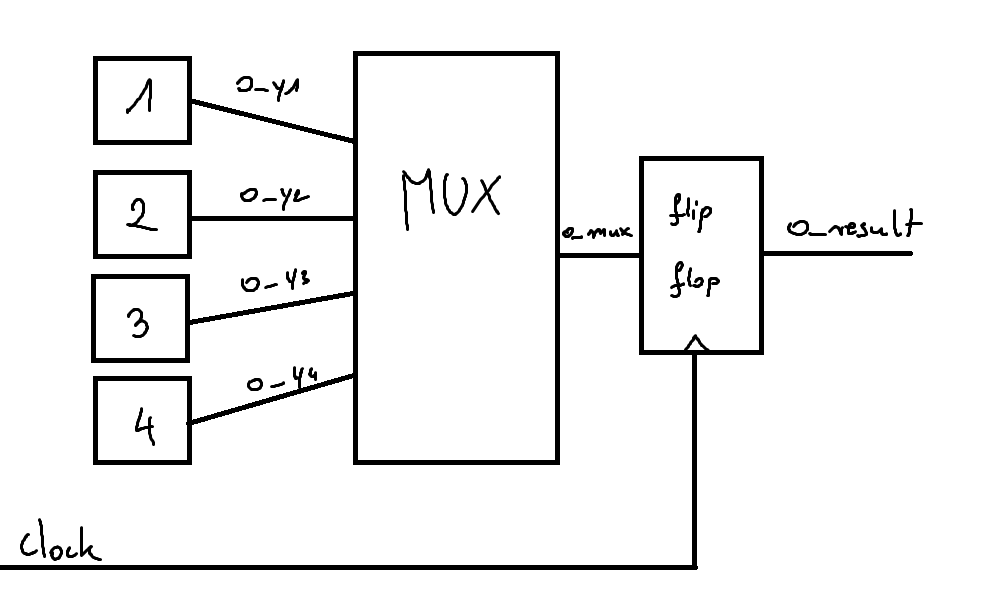

It has 2 multiplexers and 1 flip-flop (this flip-flop is in always_ff)

So it looks like that :

sorry for this stupid question. I just don't know how the yosys will create a multiplexer with a clock input, when I couldn't find anywhere in the internet any schematics on how it looks like. In other words I don't know how to create mux that is synchronized without additional flip-flop on the output.

Because I only found typical multiplexer without clock, but this code says that the multiplexer has a clock. How to make multiplexer with clock ?

I do have a problem understanding this code :

It looks like as if the multiplexer (which is this "case" here) is something like synchronized mux like here:

Something like that exist ? I couldn't find something like that on the website.

But my code looks a bit different more logical

It has 2 multiplexers and 1 flip-flop (this flip-flop is in always_ff)

So it looks like that :

sorry for this stupid question. I just don't know how the yosys will create a multiplexer with a clock input, when I couldn't find anywhere in the internet any schematics on how it looks like. In other words I don't know how to create mux that is synchronized without additional flip-flop on the output.

Because I only found typical multiplexer without clock, but this code says that the multiplexer has a clock. How to make multiplexer with clock ?