Enshuo

Junior Member level 2

Hi all,

I study a two CPU system. There is some control signals from CPU -> CPLD -> BMC. The input voltage of both CPU to CPLD and CPLD to BMC is 3.3V and the same signal, but the pull-up resistor is 4.7K from CPU to CPLD, and the pull-up resistor is 10K from CPLD to BMC. Furthermore, one resistor is pull-down at CPU0 and another is still pull-up.

So,

1. How to design the resistor and pull-up or pull-down?

2. Should active LOW be used pull-up resistor?

For example:

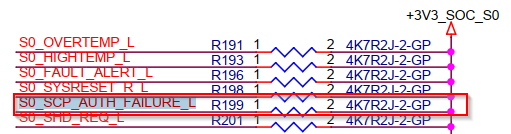

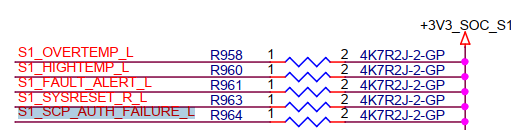

1. From CPU to CPLD, S0_SCP_AUTH_FAILURE_L and S1_SCP_AUTH_FAILURE_L are for secure boot function. They're pull-up 4.7K (active LOW).

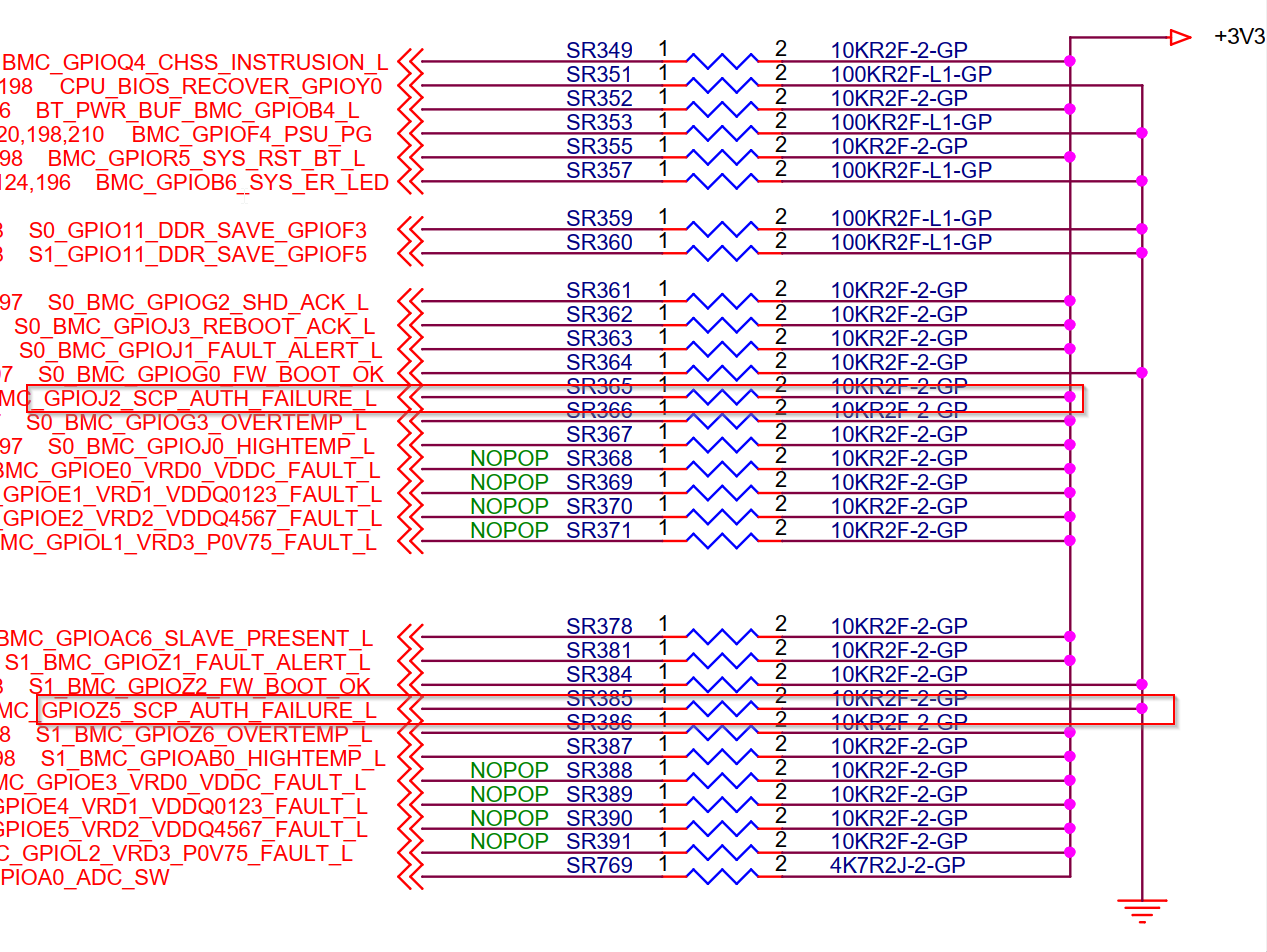

2. From CPLD to BMC, S0_BMC_GPIOJ2_SCP_AUTH_FAILURE_L is pull-up 10K, and S1_BMC_GPIOZ5_SCP_AUTH_FAILURE_L is pull-down 10K.

Why is same function with different resistors and pull-types?

I study a two CPU system. There is some control signals from CPU -> CPLD -> BMC. The input voltage of both CPU to CPLD and CPLD to BMC is 3.3V and the same signal, but the pull-up resistor is 4.7K from CPU to CPLD, and the pull-up resistor is 10K from CPLD to BMC. Furthermore, one resistor is pull-down at CPU0 and another is still pull-up.

So,

1. How to design the resistor and pull-up or pull-down?

2. Should active LOW be used pull-up resistor?

For example:

1. From CPU to CPLD, S0_SCP_AUTH_FAILURE_L and S1_SCP_AUTH_FAILURE_L are for secure boot function. They're pull-up 4.7K (active LOW).

2. From CPLD to BMC, S0_BMC_GPIOJ2_SCP_AUTH_FAILURE_L is pull-up 10K, and S1_BMC_GPIOZ5_SCP_AUTH_FAILURE_L is pull-down 10K.

Why is same function with different resistors and pull-types?