xworld2008

Full Member level 4

as below:

signal a______________|-----------------------|__________________

signal b___________________|-------------------------|___________

- Ta - - Tb -

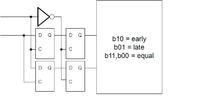

Ta,Tb are less than 100p, Ta, Tb are changing when others signals are changing, How to compare Ta and Tb(Ta > Tb ?)?

no higher clock is available.

Thanks.

signal a______________|-----------------------|__________________

signal b___________________|-------------------------|___________

- Ta - - Tb -

Ta,Tb are less than 100p, Ta, Tb are changing when others signals are changing, How to compare Ta and Tb(Ta > Tb ?)?

no higher clock is available.

Thanks.