engr_joni_ee

Advanced Member level 3

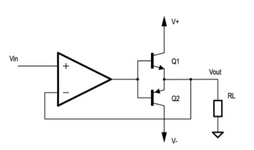

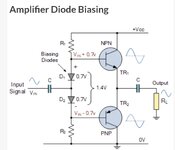

I am wondering if I have an OpAmp which can deliver maximum output current for example 50 mA and the output voltage across the load is -3 V and I need around 200 mA load current with -3 V. I found an approach to get higher output current then OpAmp. This can be done using two transistors but I am not able to understand how it work. Can someone please describe how the two transistors in the attached circuit work to get higher current ?