pskol95

Junior Member level 1

Hello Everyone,

I have inserted IO pads in the design.

I have "create_clock" command in the sdc (from synopsys dc)

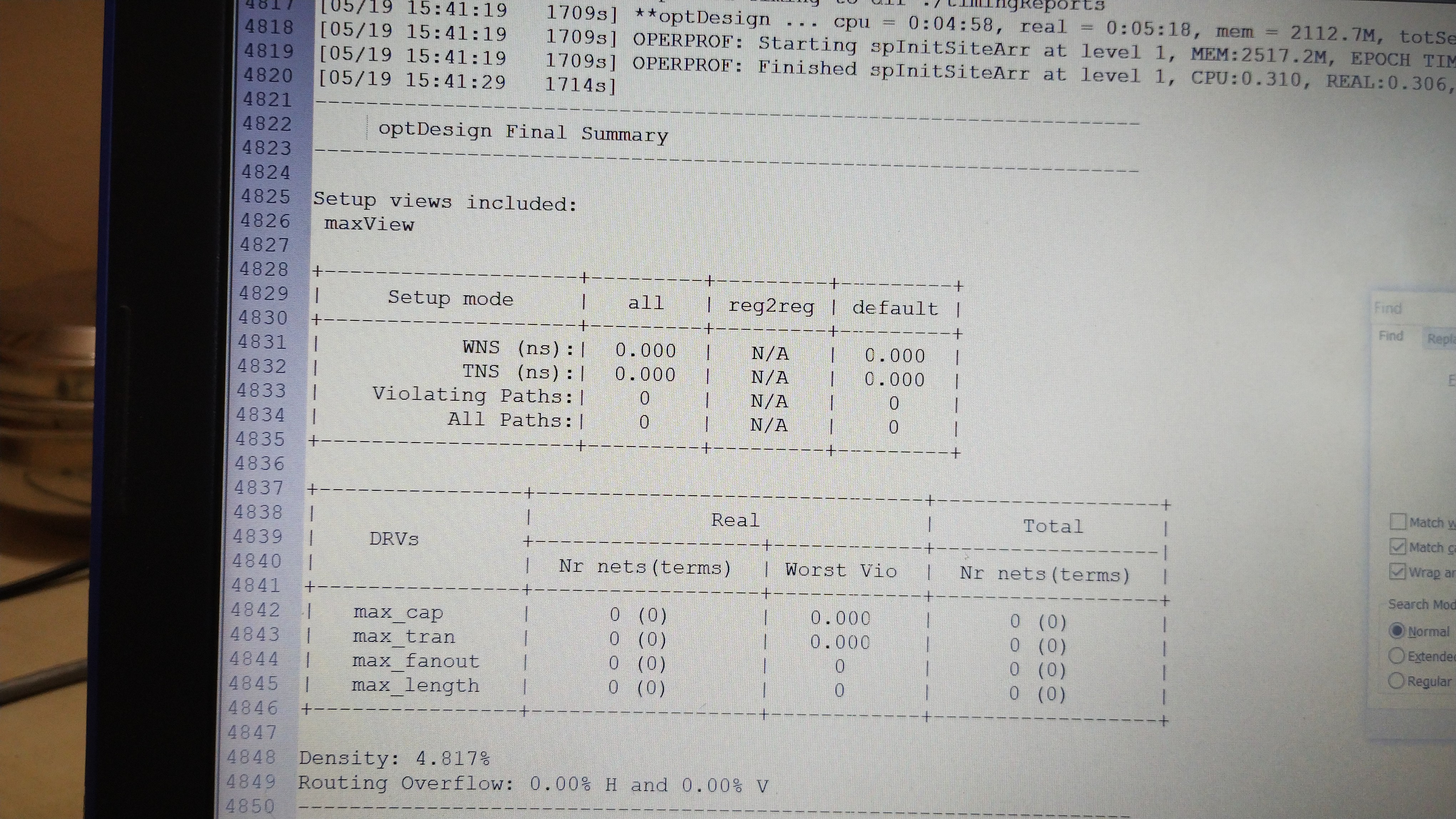

After running "optDesign -preCTS" I am getting as shown in picture.

Where am I doing mistake ?

I have inserted IO pads in the design.

I have "create_clock" command in the sdc (from synopsys dc)

After running "optDesign -preCTS" I am getting as shown in picture.

Where am I doing mistake ?