kinghero89

Junior Member level 2

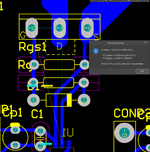

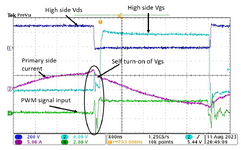

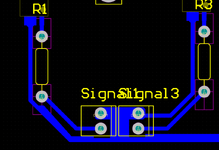

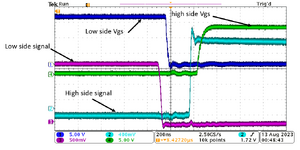

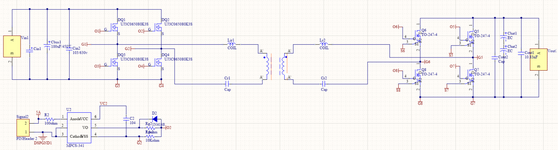

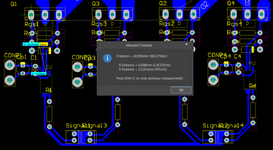

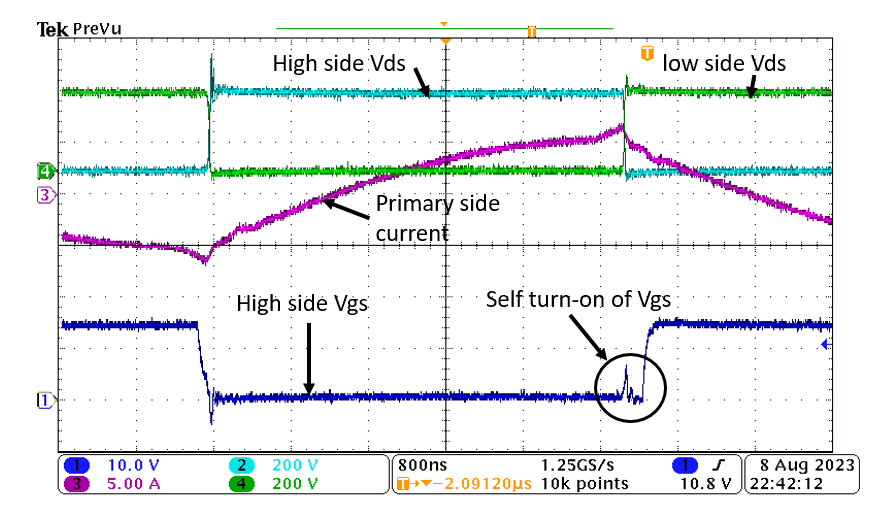

I am working on full-bridge CLLC, and the waveform I got is quite weird.

Is there anyone who has such kind of experience?

Is there anyone who has such kind of experience?