sincplicity

Newbie level 4

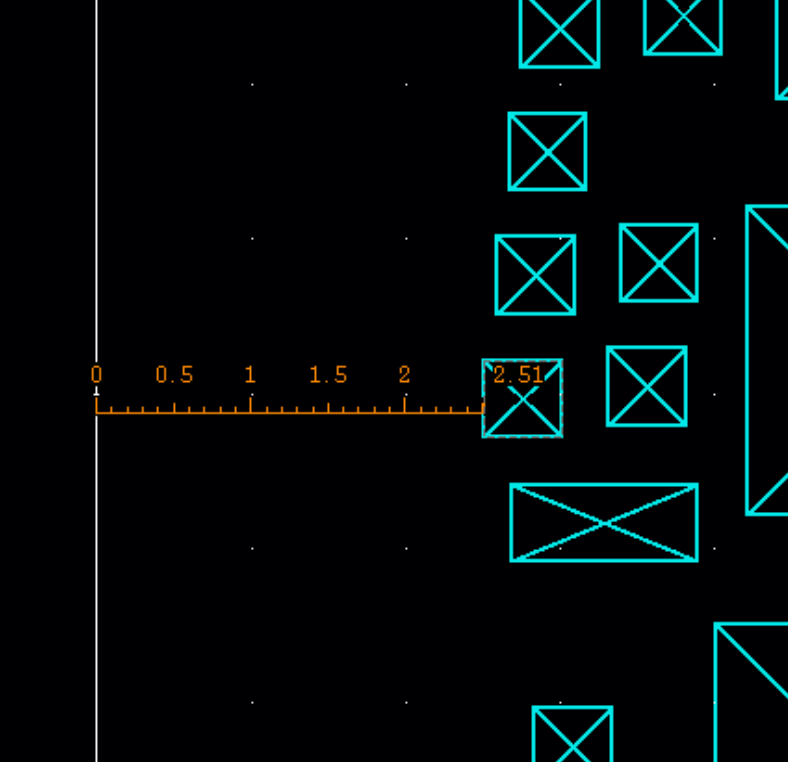

I am urgently trying to resolve some drc errors for a tsmcN65 process.

The errors are related to enclosure such as DM1.EN.1 with rule defined as:

DM1.EN.1 { @ Enclosure by chip edge >= 2.51 um

DUM1 NOT (SIZE CHIP_CHAMFERED BY -DM1_EN_1)

}

The area is defined by Pr Boundary layer. The defined edge to a violation shows >= 2.5 um distance? What am I missing?

I have requested a DRM but have not received yet. Thanks in advance!

The errors are related to enclosure such as DM1.EN.1 with rule defined as:

DM1.EN.1 { @ Enclosure by chip edge >= 2.51 um

DUM1 NOT (SIZE CHIP_CHAMFERED BY -DM1_EN_1)

}

The area is defined by Pr Boundary layer. The defined edge to a violation shows >= 2.5 um distance? What am I missing?

I have requested a DRM but have not received yet. Thanks in advance!