omar97

Newbie

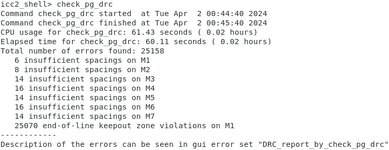

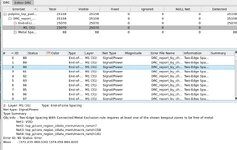

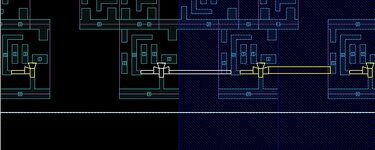

I face a problem, during powerplanning when I connect power and ground nets to power and ground pins, then when I check pg drc, I get a huge number of drc violations in metal 1 between vdd and vss metals.

The drc error is end of line keepout zone violations on metal1 inside standard cell.

I can't understand this error and I don't know how to solve it.

So please help me to understand why I face this error?

I use technology TSMC 65nm

The drc error is end of line keepout zone violations on metal1 inside standard cell.

I can't understand this error and I don't know how to solve it.

So please help me to understand why I face this error?

I use technology TSMC 65nm

Last edited by a moderator: