shanmei

Advanced Member level 1

My DLL input signal is 100MHz (10nS), and it has ten delay stages, with each stage delays 1nS. The delay stage is a basic current starving architecture with a pmos and nmos current source to control the current.

The top architecture is shown in the bellowing figure:

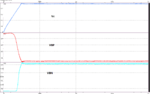

The control voltage at Vc, VBP, and VBN are shown in the bellowing figure:

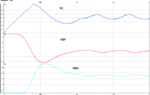

I want to reduce the spikes at VBP and VBN, so I add a 10pF capacitor on node VBP and VBN respectively, but the control voltage starts to oscillate as shown in the bellowing figure. Then I changed the 10 pF capacitor filter to low pass filter (a 10kHz resisor and a 10pF capacitor), which still presents big swing on the control nodes.

I have several questions:

1. Why it is oscillating by adding a capacitor on the bias nodes?

2. Should the DLL be unconditional stable?

3. If it is not unconditional stable, what should I to to prevent oscillation? Any formula to design those parameters?

Thanks.

The top architecture is shown in the bellowing figure:

The control voltage at Vc, VBP, and VBN are shown in the bellowing figure:

I want to reduce the spikes at VBP and VBN, so I add a 10pF capacitor on node VBP and VBN respectively, but the control voltage starts to oscillate as shown in the bellowing figure. Then I changed the 10 pF capacitor filter to low pass filter (a 10kHz resisor and a 10pF capacitor), which still presents big swing on the control nodes.

I have several questions:

1. Why it is oscillating by adding a capacitor on the bias nodes?

2. Should the DLL be unconditional stable?

3. If it is not unconditional stable, what should I to to prevent oscillation? Any formula to design those parameters?

Thanks.