Narcisuss the Reborn

Newbie level 4

Hello!

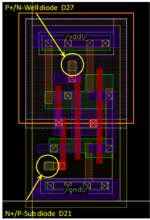

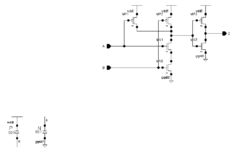

I have a problem with LVS checking of my design with Calibre Interactive. I am sure that the problem is that Calibre (I use 2021.1 version) do not extract diodes (N+ / P-Sub and P+ / N-Well) from the layout by default. So LVS (Comparison Results) reports about Discrepancies - Incorrect Instances (** missing instance **). If I cut off diodes in netlist there are not any LVS errors.

Moreover there are 66 diodes in my circuit but there are only 23 messages about missing diodes.

Notably that it is Calibre problem rather than design because I checked the very cell and have been reported by the same errors.

I also think this is Calibre setup feature because I’ve read that there is Extract Diodes option in the other Calibre versions in Customization Settings menu. But there is not such menu in my version at all!

Could someone to help me with setting up Calibre to correctly extract diodes from layout?

I have a problem with LVS checking of my design with Calibre Interactive. I am sure that the problem is that Calibre (I use 2021.1 version) do not extract diodes (N+ / P-Sub and P+ / N-Well) from the layout by default. So LVS (Comparison Results) reports about Discrepancies - Incorrect Instances (** missing instance **). If I cut off diodes in netlist there are not any LVS errors.

Moreover there are 66 diodes in my circuit but there are only 23 messages about missing diodes.

Notably that it is Calibre problem rather than design because I checked the very cell and have been reported by the same errors.

I also think this is Calibre setup feature because I’ve read that there is Extract Diodes option in the other Calibre versions in Customization Settings menu. But there is not such menu in my version at all!

Could someone to help me with setting up Calibre to correctly extract diodes from layout?