vaibhavwaman

Newbie level 4

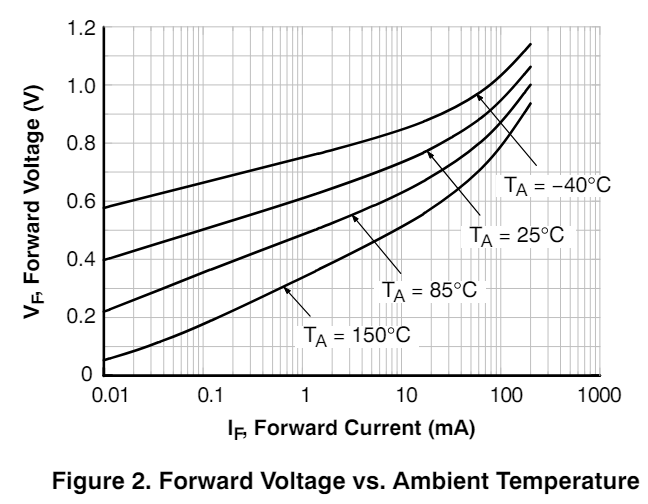

Is making linear approximation for calculating forward voltage drop at lower current than 10uA is good option ? I want to pass current approximately 100nA via this diode and want to understand forward voltage drop in this case ? Or is their any specific reason for which datasheet dont give forward voltage value for very low forward current ?