Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

Likely the current source is pulling the current through the transistor substrate diodes from ground.

In a simulation, if you use a current source, then it will do whatever it takes to generate that current.

In this case, that apparently means pulling it through the substrate diodes of the bottom transistors.

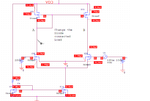

View attachment 139717

My current source is 50uA

but the drain current of M16, M29 is only 3.09uA. They don't add up to 50uA.

Where are the rest of current go?

how to increase the current on the right side of current mirror. pA is too small for the differential amplifier. this referring to the diagram above.

Is your Current Mirror working standalone ?? I mean, if you connect the second MOS to VDD directly, does it work ??

First point, you have solved the problem addressed in the question title, no forward biased substrate junction and currents are "adding up" as expected.

Secondly you are continuing what you already did in the previous thread https://www.edaboard.com/showthread.php?t=369095

Overloading the differential pair with 1.5V differential input and wondering why some are turned fully off, while others are turned with zero Vds because the capacitive load can't sink static current. That's how switch circuits work.

I don't have capacitive load on this on. The diff amp still drawing only 6.581pA, what's the reason?

View attachment 139744

Because M16 has no bias voltage (Vgs) so the drain does not draw any current.Unfortunately you connected the upper current mirror that is controlled by M24 that is connected to M16 in series.So briefly, M24 controls the mirror current and when its drain current is zero due to M16, the other current on the second branch compulsorily won't source any current.

Bias M16 with a voltage that is greater than Vt.

According to text book, {blah blah}

You changed capacitive load into no load, the effect is the same, the amplifier can't source output current. If you connect a resistive load biased to Vdd/2, you get current.I don't have capacitive load on this on. The diff amp still drawing only 6.581pA, what's the reason?

You can't expect this circuit to work as a small signal

amplifier when you have jacked the input with a large

signal. Determine when the input linear region is (once

you have fixed common mode range / biasing issues

and then try simulating as an amplifier. What you've

got here is a poor quality comparator, way overdriven.

You can't expect it to work when the left side of the

pair has zero Vgs and cuts out the PMOS mirror master.

The NMOS sink can't pull any current through the left

side, and the right side is buried (you do not see this

because you do not display the "output" node voltage.

Your NMOS mirror is run at way too high a gate voltage

(trying to stuff more current down a nonfunctional

diff pair, I expect) - back off, a lot.

Try putting the inputs at about 2V common mode with

(say) a 10mV sine difference.

There's something wrong about the results, no way

should those two drain nodes be exactly 2.00V, both.

You might want to look at the "guts" of those MbreakN

symbols and be sure they are not able to short G to D

(or, some implicit net naming mess-up?).

Annotating the voltages might help your debug.