yefj

Advanced Member level 4

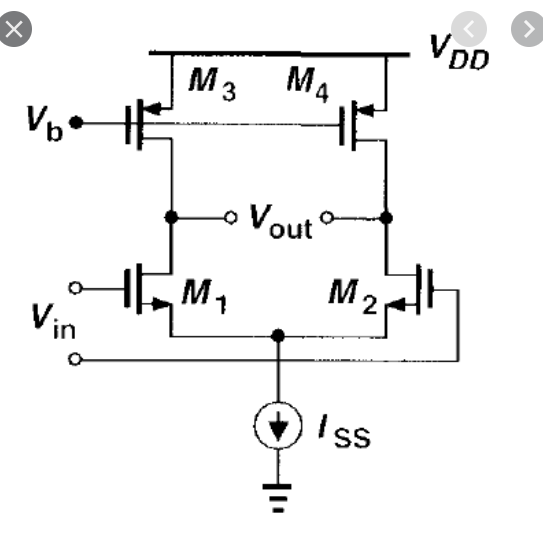

Hello,In the curcuit bellow Iss is implemented by a current mirror.

We bias the curcuit so every transistr will be in saturation which is accomplished by imagining the voltage drop on every circuit.

then we need to set the gm of M2 and Rout of M4 and C_L to set the small signal response of gain and bandwidth.

I am used to do it by tweeking which is not an engenerring way.

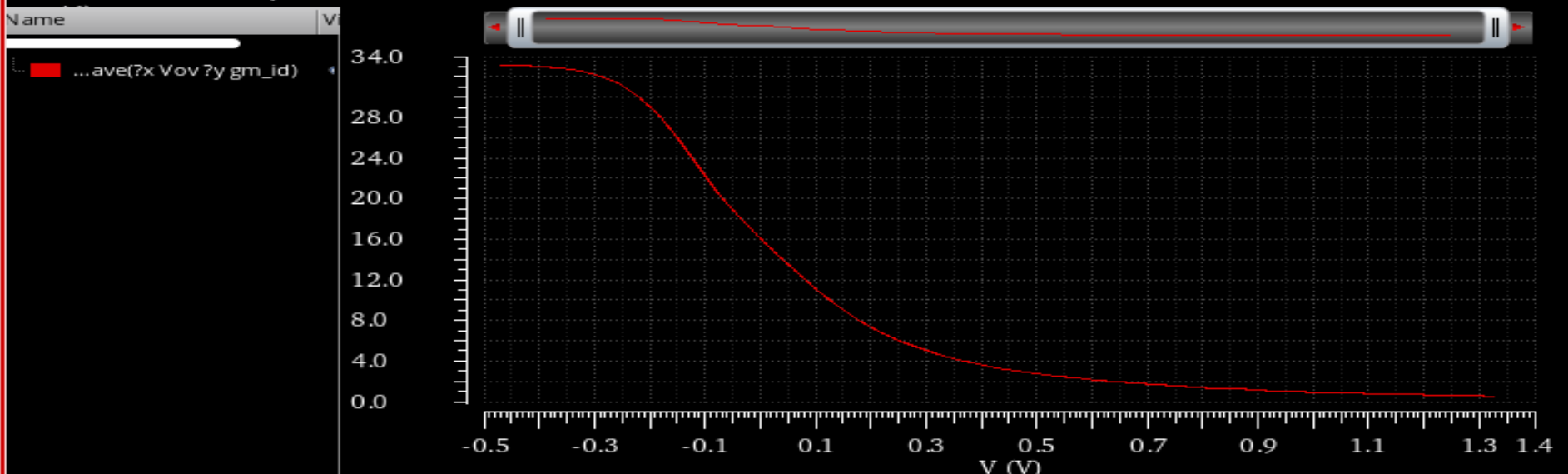

Bellow we have a gm/Id VS Vov plot of my gpdk transistor .

But we have here voltage divider Rout from two transistors in parralel,i dont know how to accomlish these tasks with gm/id plot.

Could you please tell me the general direction how to design gain bandwidth and bias using gm/id?

We bias the curcuit so every transistr will be in saturation which is accomplished by imagining the voltage drop on every circuit.

then we need to set the gm of M2 and Rout of M4 and C_L to set the small signal response of gain and bandwidth.

I am used to do it by tweeking which is not an engenerring way.

Bellow we have a gm/Id VS Vov plot of my gpdk transistor .

But we have here voltage divider Rout from two transistors in parralel,i dont know how to accomlish these tasks with gm/id plot.

Could you please tell me the general direction how to design gain bandwidth and bias using gm/id?