CuST0M1z3

Newbie level 6

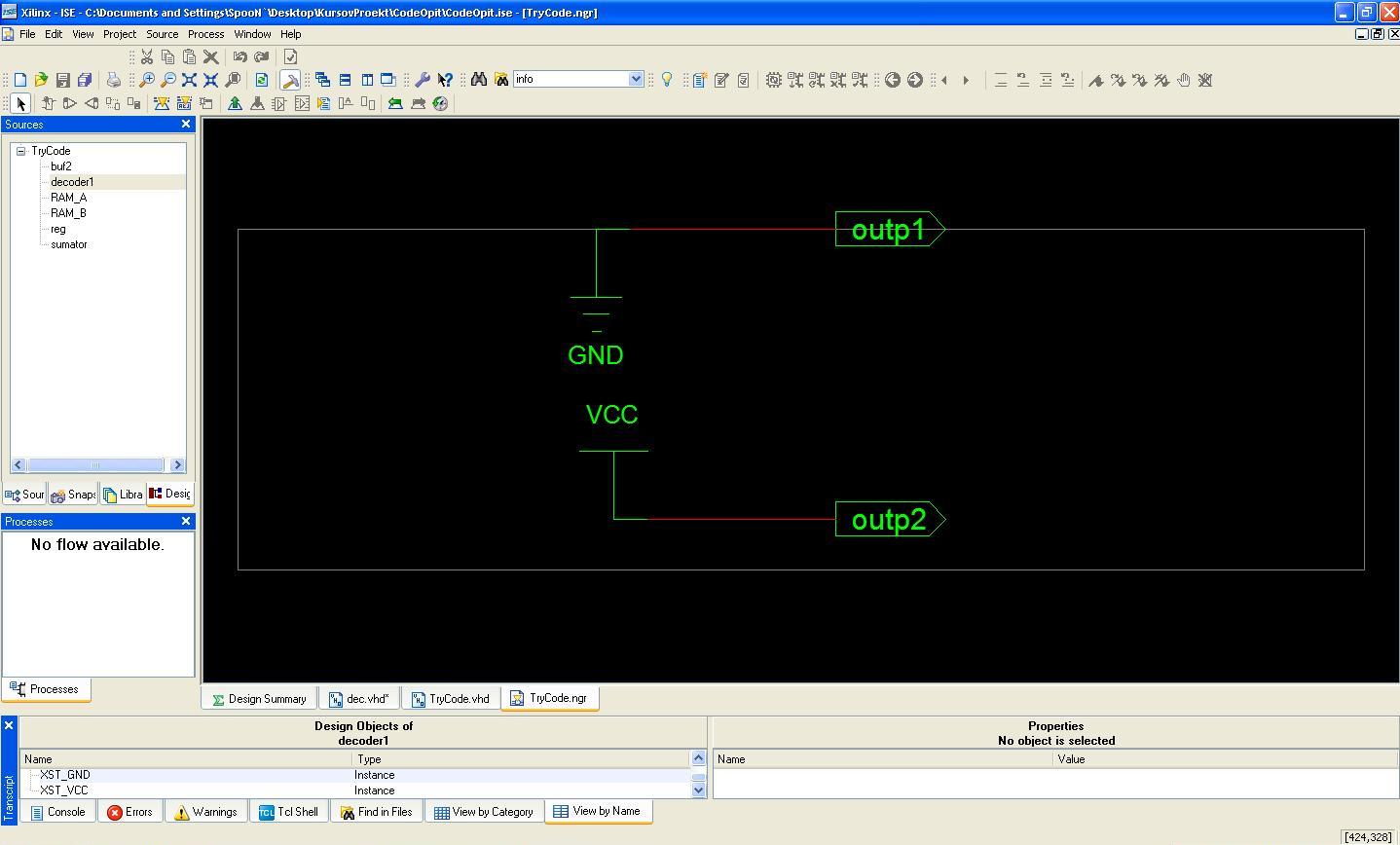

whats wrong?! ERROR - Enumerated value U is missing in case.

entity dec is

port ( din: in std_logic;

reset: in std_logic;

outp1 : out std_logic;

outp2 : out std_logic);

end dec;

architecture Behav2 of dec is

begin

process(reset,din)

begin

if (reset = '1') then

outp1 <= '0';

outp2 <= '1';

else

case din is

when '0' => outp1 <= '0';

when '1' => outp2 <= '1';

end case;

end if;

end process;

end Behav2;

entity dec is

port ( din: in std_logic;

reset: in std_logic;

outp1 : out std_logic;

outp2 : out std_logic);

end dec;

architecture Behav2 of dec is

begin

process(reset,din)

begin

if (reset = '1') then

outp1 <= '0';

outp2 <= '1';

else

case din is

when '0' => outp1 <= '0';

when '1' => outp2 <= '1';

end case;

end if;

end process;

end Behav2;