dawson

Member level 1

Hi,

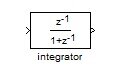

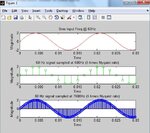

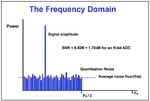

I need to generate a 1st order sigma delta ADC and run the simulation of the output. values can vary. I need a guide to use which software to allow me to perform the model simulation.

currently i've found out others using Matlab, Circuit maker, Labview. Which 1 is a better option and anyone have any similair examples for me to references.

Required urgent support thanks.

Dawson

I need to generate a 1st order sigma delta ADC and run the simulation of the output. values can vary. I need a guide to use which software to allow me to perform the model simulation.

currently i've found out others using Matlab, Circuit maker, Labview. Which 1 is a better option and anyone have any similair examples for me to references.

Required urgent support thanks.

Dawson