fred3991

Member level 1

Hello!

I want to create an EM substrate for electromagnetic simulation in Keysight ADS and would like some advice on how this can be done correctly.

Initially I only had the information from the Desigh Rule Manual(DRM) for CMOS technology.

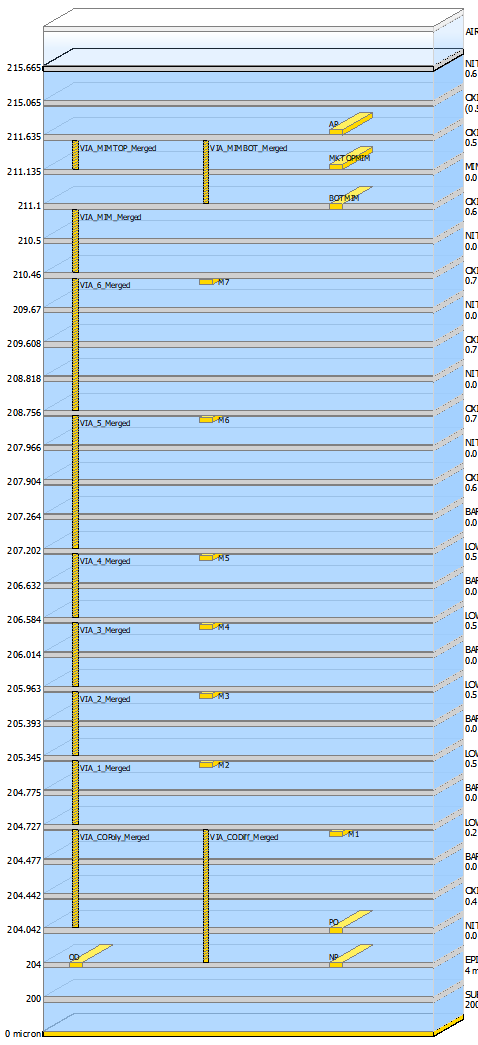

Using the information on the internet and the substrate files for ADS other technologies (.ltd files) I created the following structure

The parameters of metal layers (thickness and conductivity) and dielectric layers (thickness and dielectric constant) were taken from the DRM.

I even found information about "derived layers" in ADS and created a merging of metal vias into one polygon (to reduce the simulation time).. https://muehlhaus.com/archives/1411

For this CMOS technology, there are real measurements of elements made at the sonde station with a vector network analyzer (microstrip lines, coils and MIM capacitors).

After several variations of selecting the thickness of dielectrics, dielectric constant, conductivity of materials, I began to get a little close results EM simulation (Momentum RF).

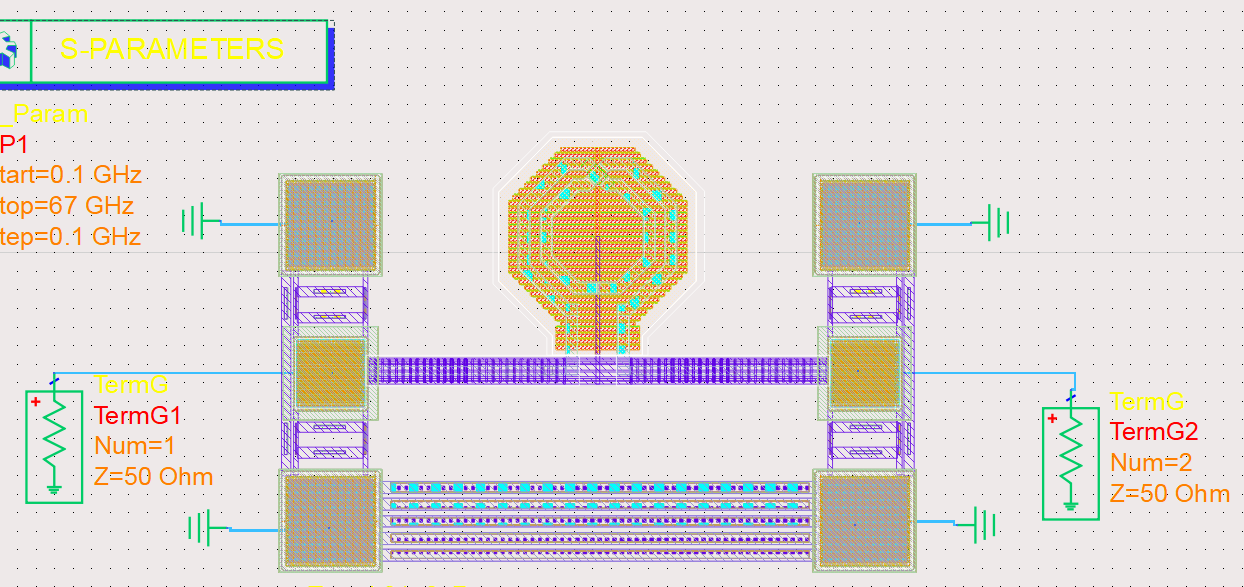

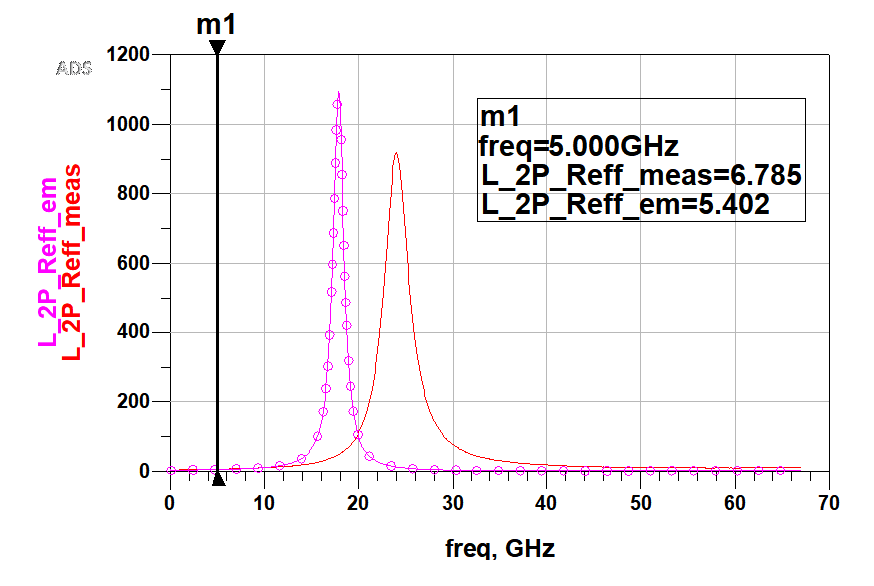

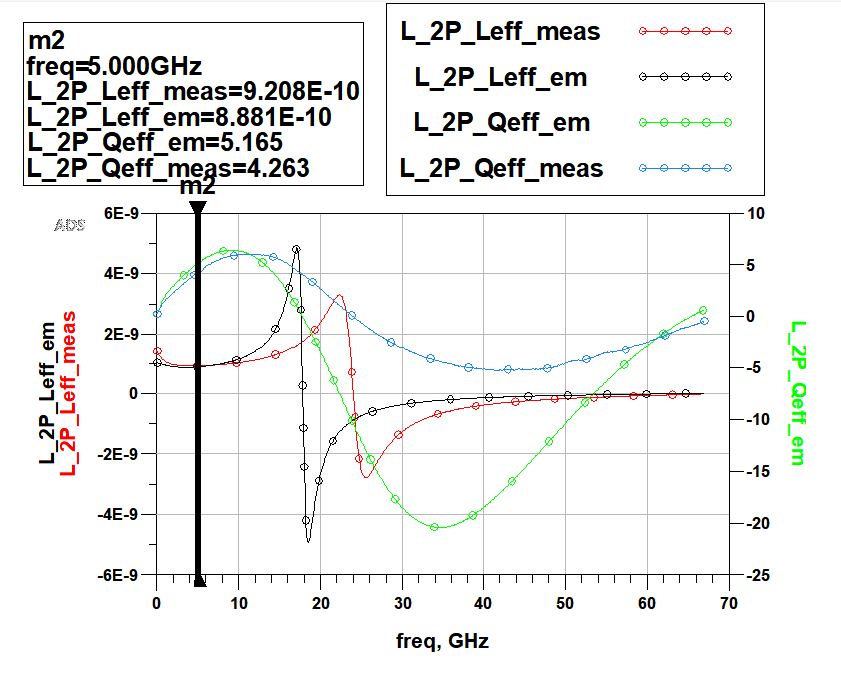

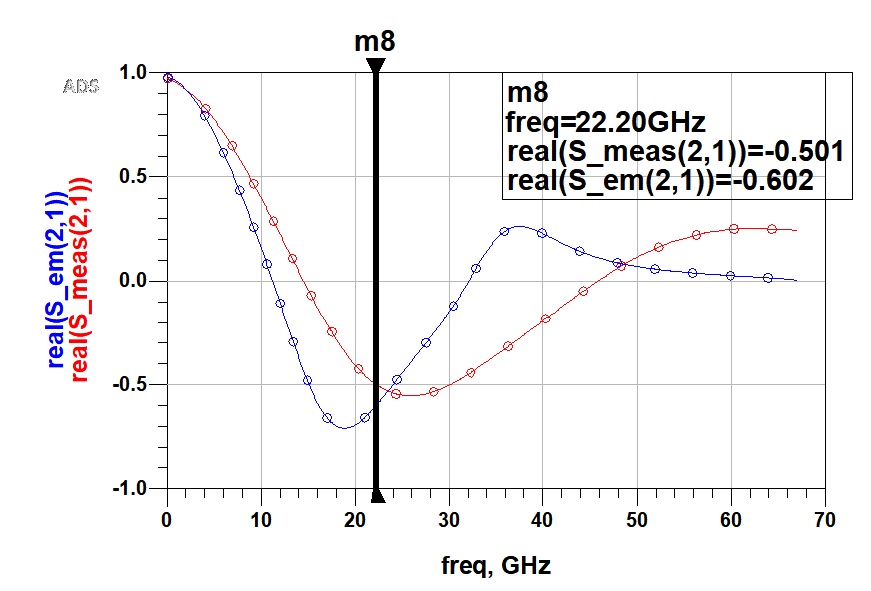

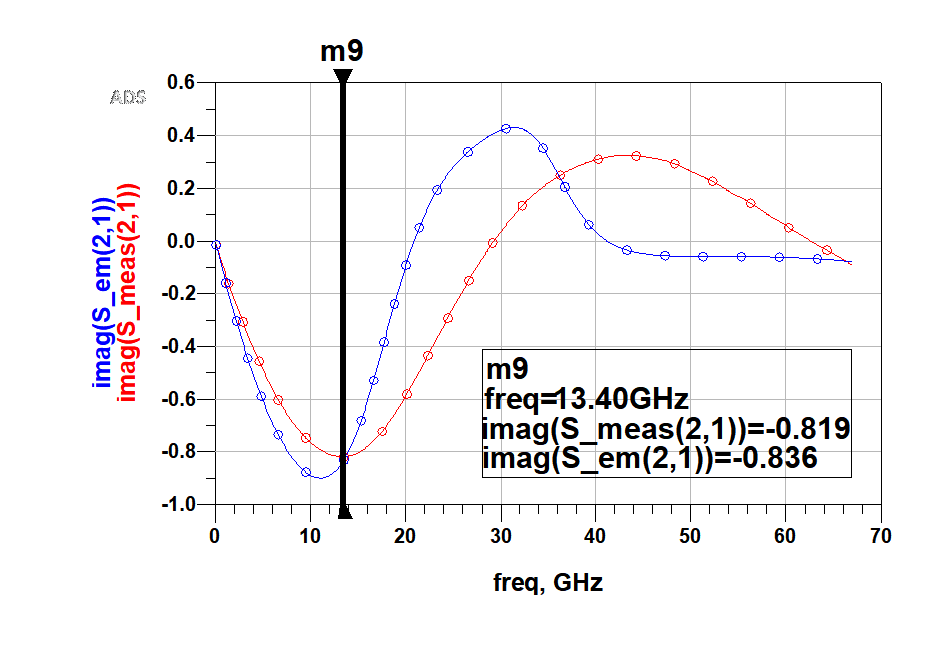

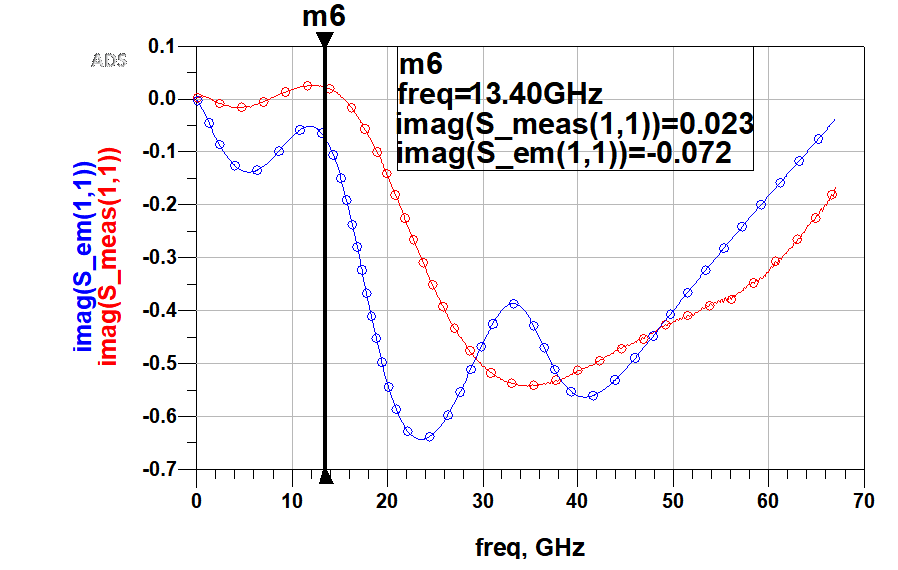

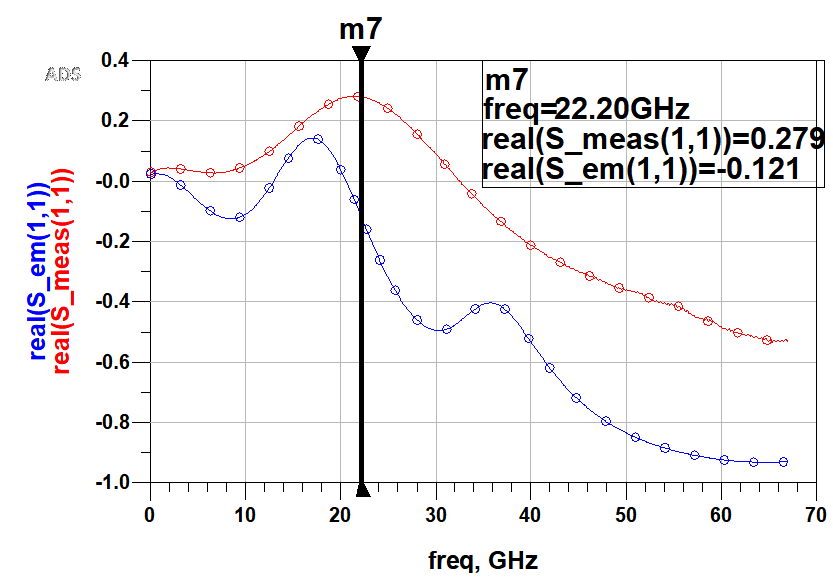

For example here - to check the EM substrate (without sparing the CPU power and my time ) I tried to simulate the inductor coil together with the pads and lines and these are the results I got.

) I tried to simulate the inductor coil together with the pads and lines and these are the results I got.

Obviously, now the substrate has too high dielectric constant (Self Res Freq should be shifted to the right).

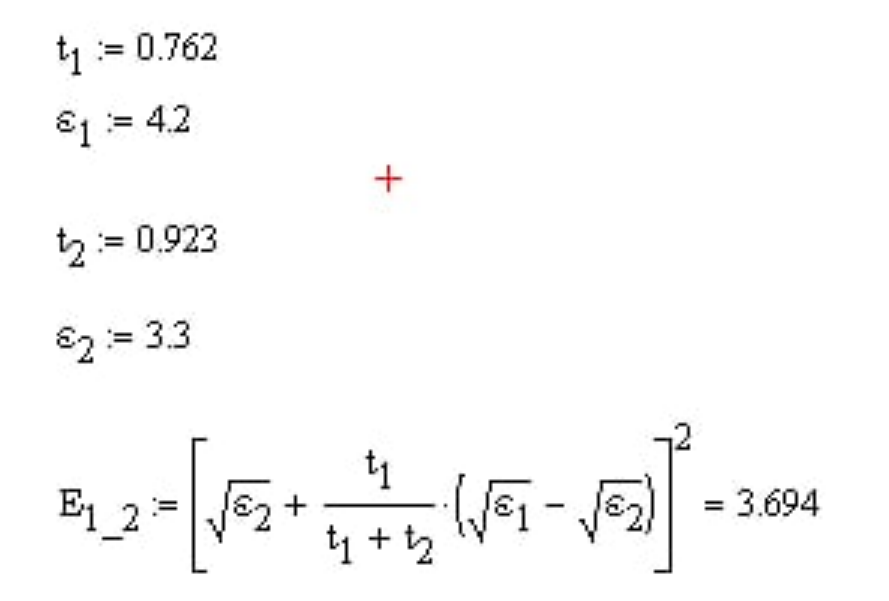

Also, as far as I know, many dielectric layers can be combined by one equivalent layer.

(by this formula?)

My questions are as follows:

What additional structures need to be fabricated and measured to accurately estimate the substrate parameters? (Perhaps baluns, line segments in individual metal layers?)

Is there any algorithm or key points for creating an EM substrate? Or is it only possible to change the substrate parameters and simulate a very large number of times until an acceptable result is obtained? only a brute-force search ?)

?)

In other words, there is no clear answer and I have to rely only on my own experience?

I want to create an EM substrate for electromagnetic simulation in Keysight ADS and would like some advice on how this can be done correctly.

Initially I only had the information from the Desigh Rule Manual(DRM) for CMOS technology.

Using the information on the internet and the substrate files for ADS other technologies (.ltd files) I created the following structure

The parameters of metal layers (thickness and conductivity) and dielectric layers (thickness and dielectric constant) were taken from the DRM.

I even found information about "derived layers" in ADS and created a merging of metal vias into one polygon (to reduce the simulation time).. https://muehlhaus.com/archives/1411

For this CMOS technology, there are real measurements of elements made at the sonde station with a vector network analyzer (microstrip lines, coils and MIM capacitors).

After several variations of selecting the thickness of dielectrics, dielectric constant, conductivity of materials, I began to get a little close results EM simulation (Momentum RF).

For example here - to check the EM substrate (without sparing the CPU power and my time

Obviously, now the substrate has too high dielectric constant (Self Res Freq should be shifted to the right).

Also, as far as I know, many dielectric layers can be combined by one equivalent layer.

(by this formula?)

My questions are as follows:

What additional structures need to be fabricated and measured to accurately estimate the substrate parameters? (Perhaps baluns, line segments in individual metal layers?)

Is there any algorithm or key points for creating an EM substrate? Or is it only possible to change the substrate parameters and simulate a very large number of times until an acceptable result is obtained? only a brute-force search

In other words, there is no clear answer and I have to rely only on my own experience?