vamsi57

Newbie level 4

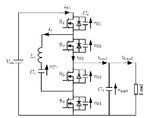

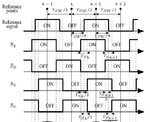

I want to design a control circuit for switched capacitor resonant converter with phase shift control having four mosfet switches.The gating pulses to the mosfets are given with a phase shift...as shown...

switching frequency is 20KHz and the.....and the phase shift for first 2 switched lags...phase lead for the next 2 switches...

so,i need help in designing the control circuit to produce pulses as shown above......

switching frequency is 20KHz and the.....and the phase shift for first 2 switched lags...phase lead for the next 2 switches...

so,i need help in designing the control circuit to produce pulses as shown above......