yefj

Advanced Member level 4

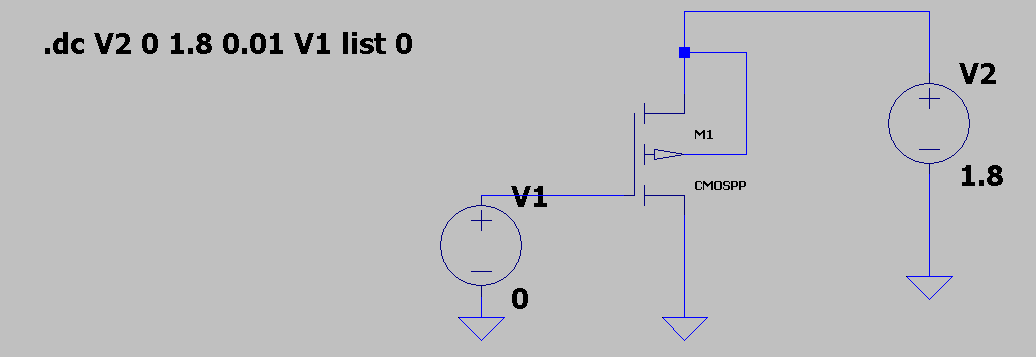

Hello,I am using a Pmosfet with netlist from this

https://sanjayvidhyadharan.in/Downloads/tsmc_180_nm/tsmc018.lib

saturation is Vds>Vgs-V_th

linear is Vds>Vgs-V_th

Could you guide me with what exact plots to do in order t see the cutoff saturation linear regions?

Thanks.

https://sanjayvidhyadharan.in/Downloads/tsmc_180_nm/tsmc018.lib

saturation is Vds>Vgs-V_th

linear is Vds>Vgs-V_th

Could you guide me with what exact plots to do in order t see the cutoff saturation linear regions?

Thanks.