Monady

Advanced Member level 4

Hello,

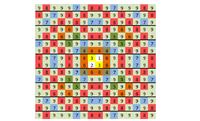

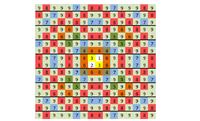

I am looking for a common centroid layout for a binary weighted DAC and in a thesis online found an arrangement, but I have had a hard time figuring out a pattern in this placement. The figure below is the capacitor array placement and each number in this figure (i= 1, ...9) shows to which capacitor (Ci) each unit cap belongs. I appreciate if someone helps me finding a pattern for this placement, since I want to use this pattern to draw layout for another DAC with different resolution.

Thanks

I am looking for a common centroid layout for a binary weighted DAC and in a thesis online found an arrangement, but I have had a hard time figuring out a pattern in this placement. The figure below is the capacitor array placement and each number in this figure (i= 1, ...9) shows to which capacitor (Ci) each unit cap belongs. I appreciate if someone helps me finding a pattern for this placement, since I want to use this pattern to draw layout for another DAC with different resolution.

Thanks