e-potis

Newbie level 4

Dear all,

This is probably not the right forum to post my issue, but it is seemed to be the most relevant.

I am interfacing a Xilinx ML506 board with a texas instrument parallel TI DAC evaluation board using a breakout board I designed. Both boards have header rows which I match on my pcb.

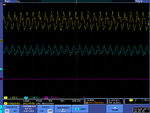

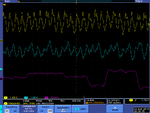

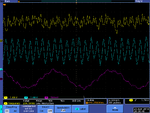

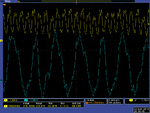

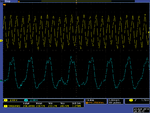

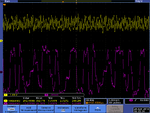

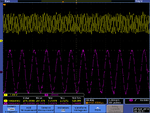

I am having issues with clock to the DAC, which I run at 275MHz,but have tried lower frequencies. It has a phase difference of 180 to the data lines, but I have tried all 90 degrees variations. The output of the DAC has phase noise at best and looks random at worst. I know it's the clock because I have found a way around the issue -getting a differential clock output and then converting it using an LVDS to CMOS converter - and it works fine. Also random trickery like putting a cap between the clock and ground sometimes work.

I have the Digital and Analogue supplies shorted on the DAC boards and it's powered from the FPGA board. My constrain for the clock is | IOSTANDARD=LVTTL | DRIVE=12 | SLEW = FAST;

Any solutions/ideas/clues would be greatly appreciated, as this is baffling me for quite a while now. I can provide schematics, scope grabs and any other kind of data you think could help you help me.

Thank you in advance

George

This is probably not the right forum to post my issue, but it is seemed to be the most relevant.

I am interfacing a Xilinx ML506 board with a texas instrument parallel TI DAC evaluation board using a breakout board I designed. Both boards have header rows which I match on my pcb.

I am having issues with clock to the DAC, which I run at 275MHz,but have tried lower frequencies. It has a phase difference of 180 to the data lines, but I have tried all 90 degrees variations. The output of the DAC has phase noise at best and looks random at worst. I know it's the clock because I have found a way around the issue -getting a differential clock output and then converting it using an LVDS to CMOS converter - and it works fine. Also random trickery like putting a cap between the clock and ground sometimes work.

I have the Digital and Analogue supplies shorted on the DAC boards and it's powered from the FPGA board. My constrain for the clock is | IOSTANDARD=LVTTL | DRIVE=12 | SLEW = FAST;

Any solutions/ideas/clues would be greatly appreciated, as this is baffling me for quite a while now. I can provide schematics, scope grabs and any other kind of data you think could help you help me.

Thank you in advance

George