GiGa212

Newbie

Hi all!

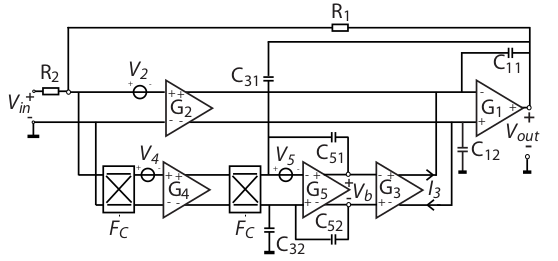

I'm a Jr. Analog IC Designer that are trying to design, for the first time, a chopper amplifier based on the following structure:

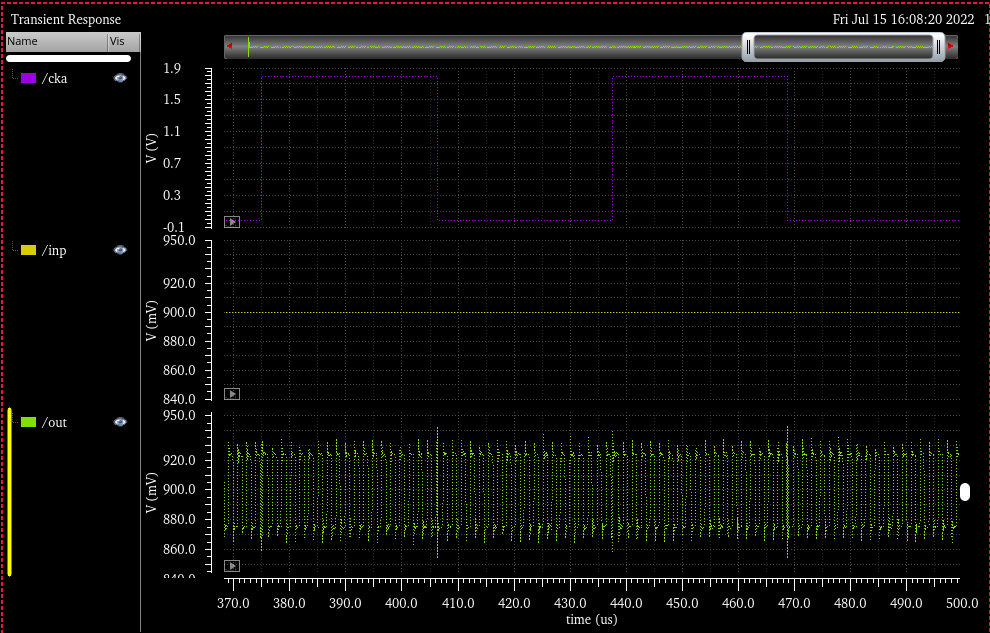

I've already designed all blocks, and now I'm simulating the entire system (transient, pss, etc.) in buffer mode, with a DC input equal to VDD/2, and chopper freq equal to 16kHz (that freq. is greater than the 1/f corner of the core stage G2+G1).

During transient simulation I noticed a strange behavior (I think) of the output; in practice I expect that the output should be synchronous with the chopping frequency, but in reality the behavior is the following:

My question is:

is it correct that the output oscillates faster than the chopping freq.? If yes, do you know what is the problem?

Thanks.

I'm a Jr. Analog IC Designer that are trying to design, for the first time, a chopper amplifier based on the following structure:

I've already designed all blocks, and now I'm simulating the entire system (transient, pss, etc.) in buffer mode, with a DC input equal to VDD/2, and chopper freq equal to 16kHz (that freq. is greater than the 1/f corner of the core stage G2+G1).

During transient simulation I noticed a strange behavior (I think) of the output; in practice I expect that the output should be synchronous with the chopping frequency, but in reality the behavior is the following:

My question is:

is it correct that the output oscillates faster than the chopping freq.? If yes, do you know what is the problem?

Thanks.