cupoftea

Advanced Member level 5

Hi,

I hear..

....that in an LLC converter, L(res) and C(res) should be chosen such that SQRT(Ls/Cs) = ~1.5 * "Load resistance".

...Presumably thats the "referred AC load resistance", ie 8* (Np/Ns)^2* R(out) / (pi^2)?

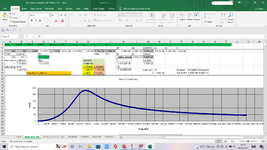

The thing is, when you do this, you end up with your intended operating frequency being very near to the peak of the gain curve....ie, the "peak of doom"...that frequency above which, you go into the dreaded "capacitive region"....so it feels more coMfortable to make SQRT(Ls/Cs) of a value nearer 1.....is this OK?

So is there any leeway in this choice of Lres and Cres?

Presumably its all about short circuit currents and overload?

I hear..

....that in an LLC converter, L(res) and C(res) should be chosen such that SQRT(Ls/Cs) = ~1.5 * "Load resistance".

...Presumably thats the "referred AC load resistance", ie 8* (Np/Ns)^2* R(out) / (pi^2)?

The thing is, when you do this, you end up with your intended operating frequency being very near to the peak of the gain curve....ie, the "peak of doom"...that frequency above which, you go into the dreaded "capacitive region"....so it feels more coMfortable to make SQRT(Ls/Cs) of a value nearer 1.....is this OK?

So is there any leeway in this choice of Lres and Cres?

Presumably its all about short circuit currents and overload?