Rohbinhoodie

Newbie level 5

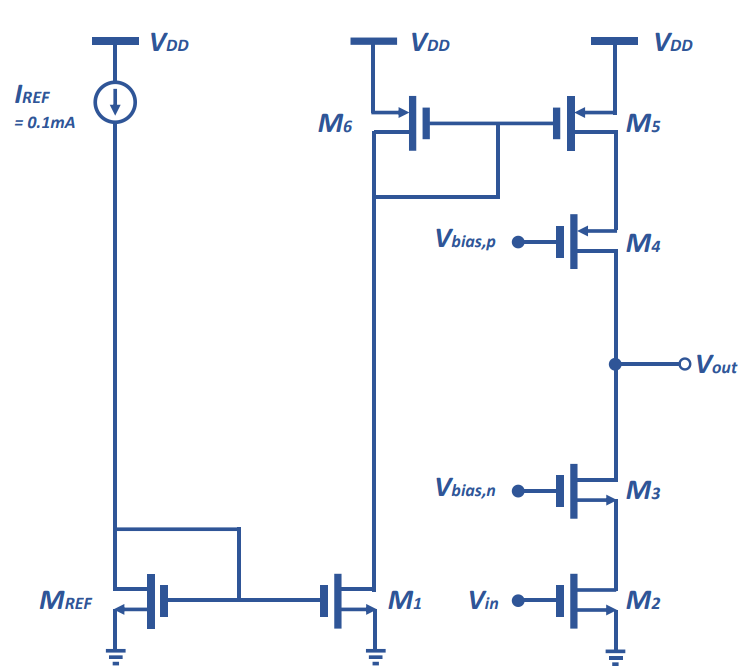

I want to make this circuit having more than 30dB voltage gain by controlling Length and width of the mosfets and biasing Vgs.

But literally I have no idea how to start with this.

Can you guys pls give me some useful tips?

+the mosfet is TSMC 180nm level 49.

+Vdd is 2.5v

+1.8um < L < 5um

+ 1.8um < w < 100um

Thank you for reading.

But literally I have no idea how to start with this.

Can you guys pls give me some useful tips?

+the mosfet is TSMC 180nm level 49.

+Vdd is 2.5v

+1.8um < L < 5um

+ 1.8um < w < 100um

Thank you for reading.

Last edited: