sawaak

Full Member level 2

Hi all,

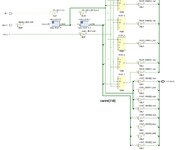

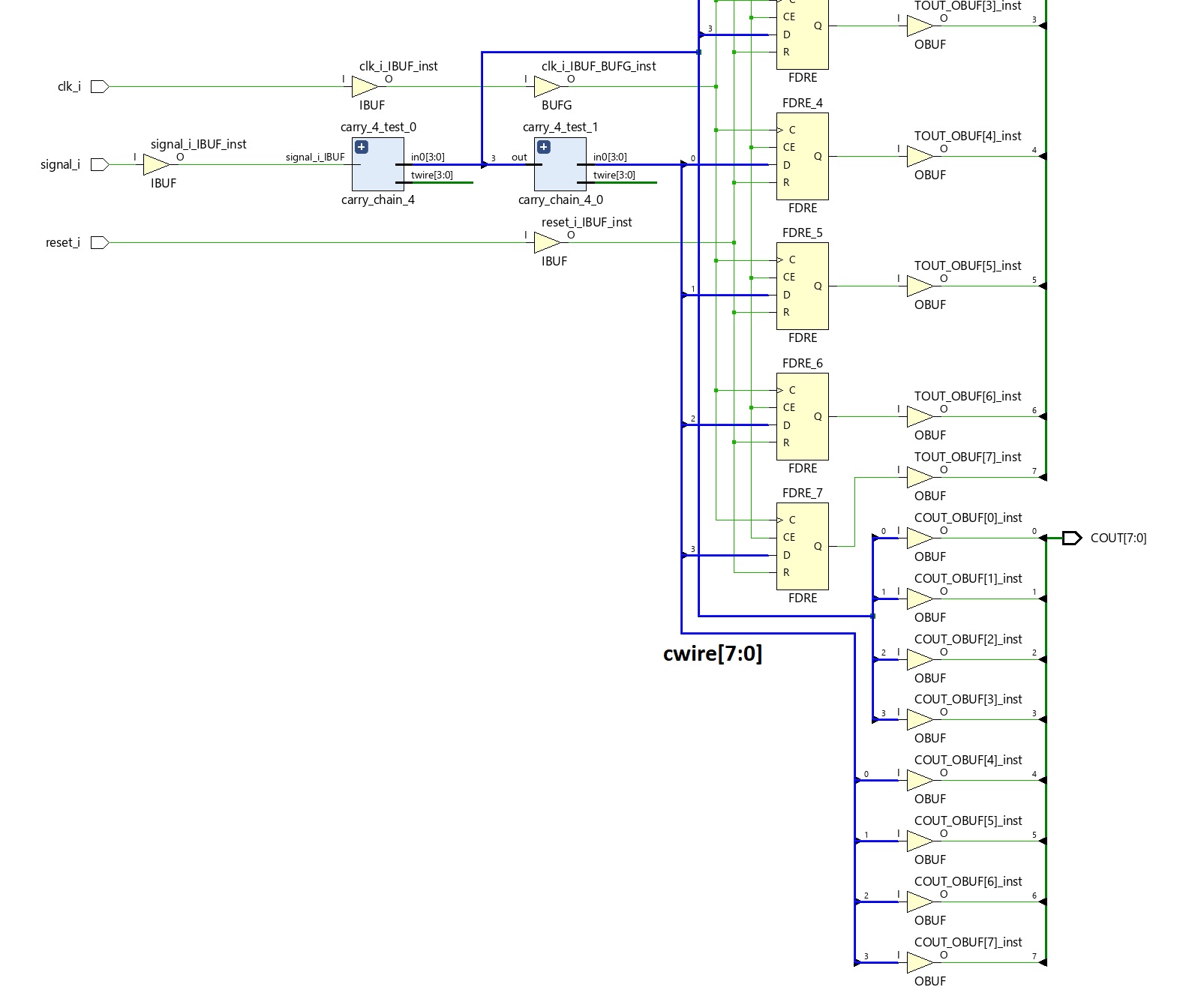

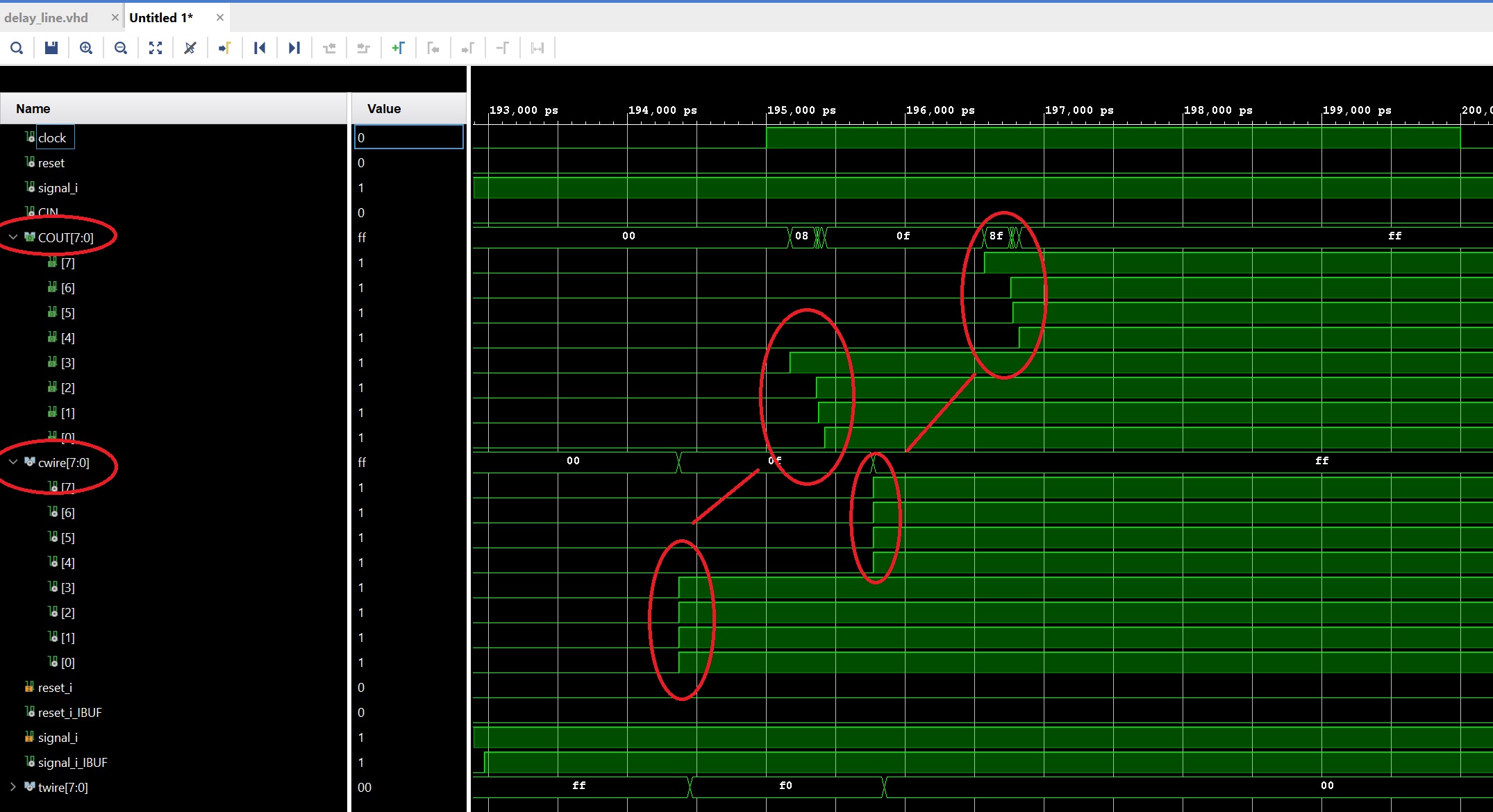

I am trying to simulate a delay line created using carry4 primitives. I am running post-synthesis timing simulation using Vivado 2021.1 and Artix-7 device. The carry4 primitive includes 4 carry logics and should have a delay associated with each of them. The problem is I am unable to observe those delays in the post-synthesis timing simulation - all carry logics associated with a particular carry4 primitive appear to have changed at the same time. I can see variable delays at the output port when I route the output to output pins which I don't want obviously when creating a TDC.

By definition, I should see the variable delays at the output of carry4 primitives (cwire[7:0] net in attached figure). Any one knows how to achieve this?

Thank you.

I am trying to simulate a delay line created using carry4 primitives. I am running post-synthesis timing simulation using Vivado 2021.1 and Artix-7 device. The carry4 primitive includes 4 carry logics and should have a delay associated with each of them. The problem is I am unable to observe those delays in the post-synthesis timing simulation - all carry logics associated with a particular carry4 primitive appear to have changed at the same time. I can see variable delays at the output port when I route the output to output pins which I don't want obviously when creating a TDC.

By definition, I should see the variable delays at the output of carry4 primitives (cwire[7:0] net in attached figure). Any one knows how to achieve this?

Thank you.