joyu

Newbie level 5

I am looking for a good resource on the negative effects of having high ripple current with a buck converter at low load.

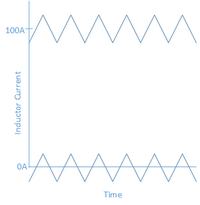

Most resources agree that you should design your ripple current around 20% of your maximum current. If you have a design with a huge swing between maximum and minimum output load current, this 20% rule can end up with significant negative inductor current when operating at the minimum output in CCM mode.

What are the adverse affects of operating in this minimum power mode with CCM?

Reasons for the 20% guideline I have read so far

-Less Current Ripple -> Less Caps (Less $)

-Less Current Ripple -> Less EMI

What I am really looking for is what kind of component failures we might see operating with this large negative current through the inductor (which will flow through to the input caps for part of the time).

Most resources agree that you should design your ripple current around 20% of your maximum current. If you have a design with a huge swing between maximum and minimum output load current, this 20% rule can end up with significant negative inductor current when operating at the minimum output in CCM mode.

What are the adverse affects of operating in this minimum power mode with CCM?

Reasons for the 20% guideline I have read so far

-Less Current Ripple -> Less Caps (Less $)

-Less Current Ripple -> Less EMI

What I am really looking for is what kind of component failures we might see operating with this large negative current through the inductor (which will flow through to the input caps for part of the time).