Hawaslsh

Full Member level 3

- Joined

- Mar 13, 2015

- Messages

- 164

- Helped

- 5

- Reputation

- 10

- Reaction score

- 7

- Trophy points

- 1,298

- Location

- Washington DC, USA

- Activity points

- 3,422

Hi all,

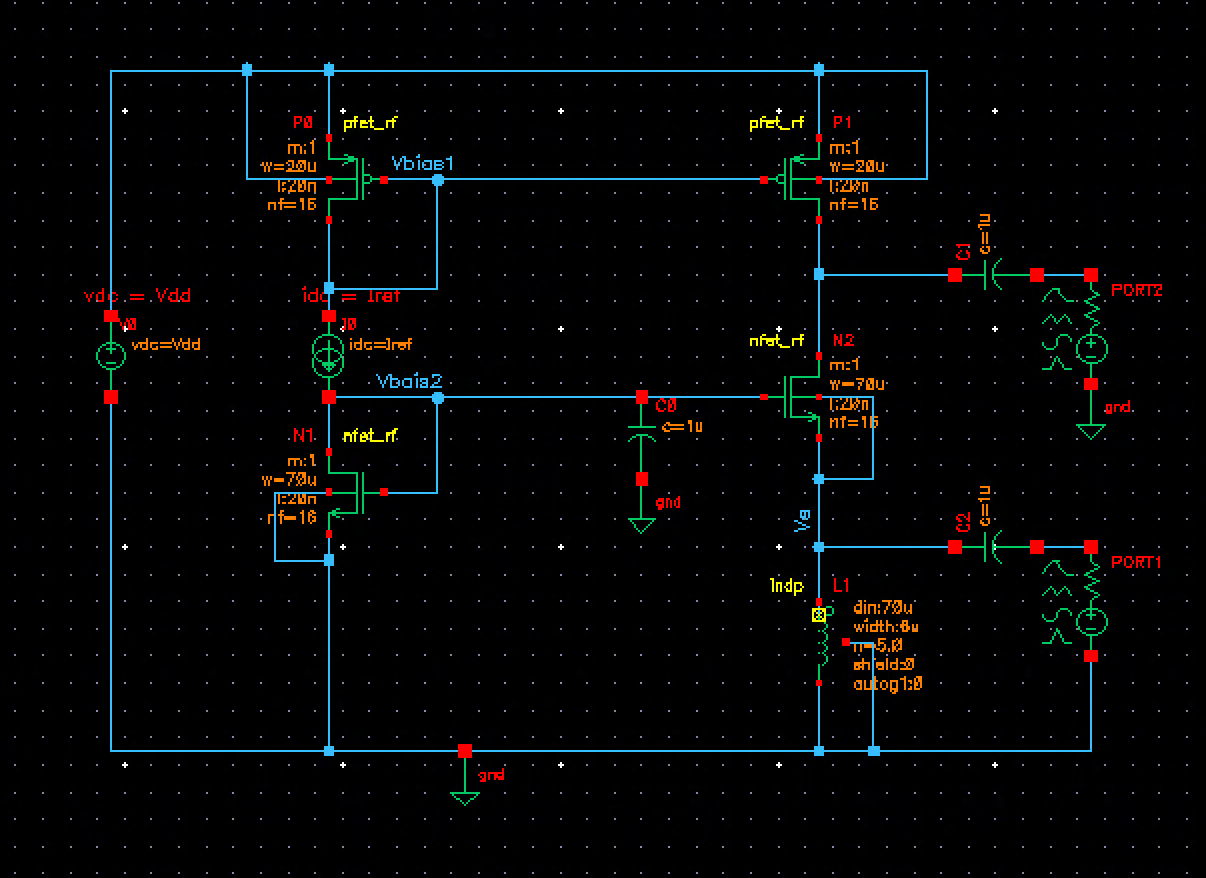

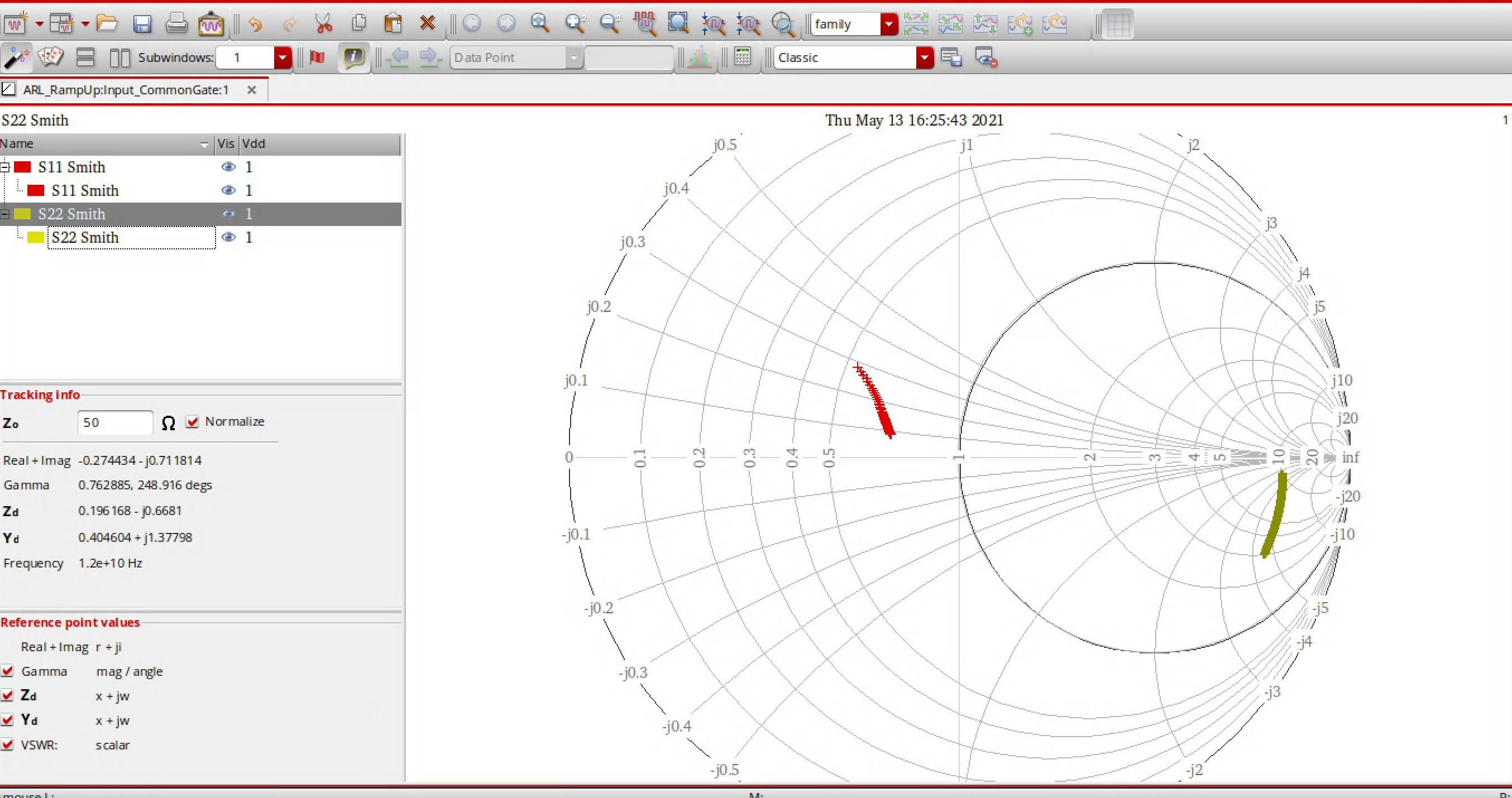

Relatively new to CMOS design so I had a pretty basic question. I am working on a common gate input stage to a amplifier. Above is the circuit schematic for the stage. I am trying to use current mirrors to set the drain current. From what I have read so far, it seems common practice to bias the PMOS current source with a current mirror to create an active load. But no examples I have read showed how to bias the gate properly. Is it bad to use a current mirror as well for the common gate biasing, or should I just use a resistive divider from Vdd? I got pretty good small signal results using this method. Id in this case was very close to Iref, as expected

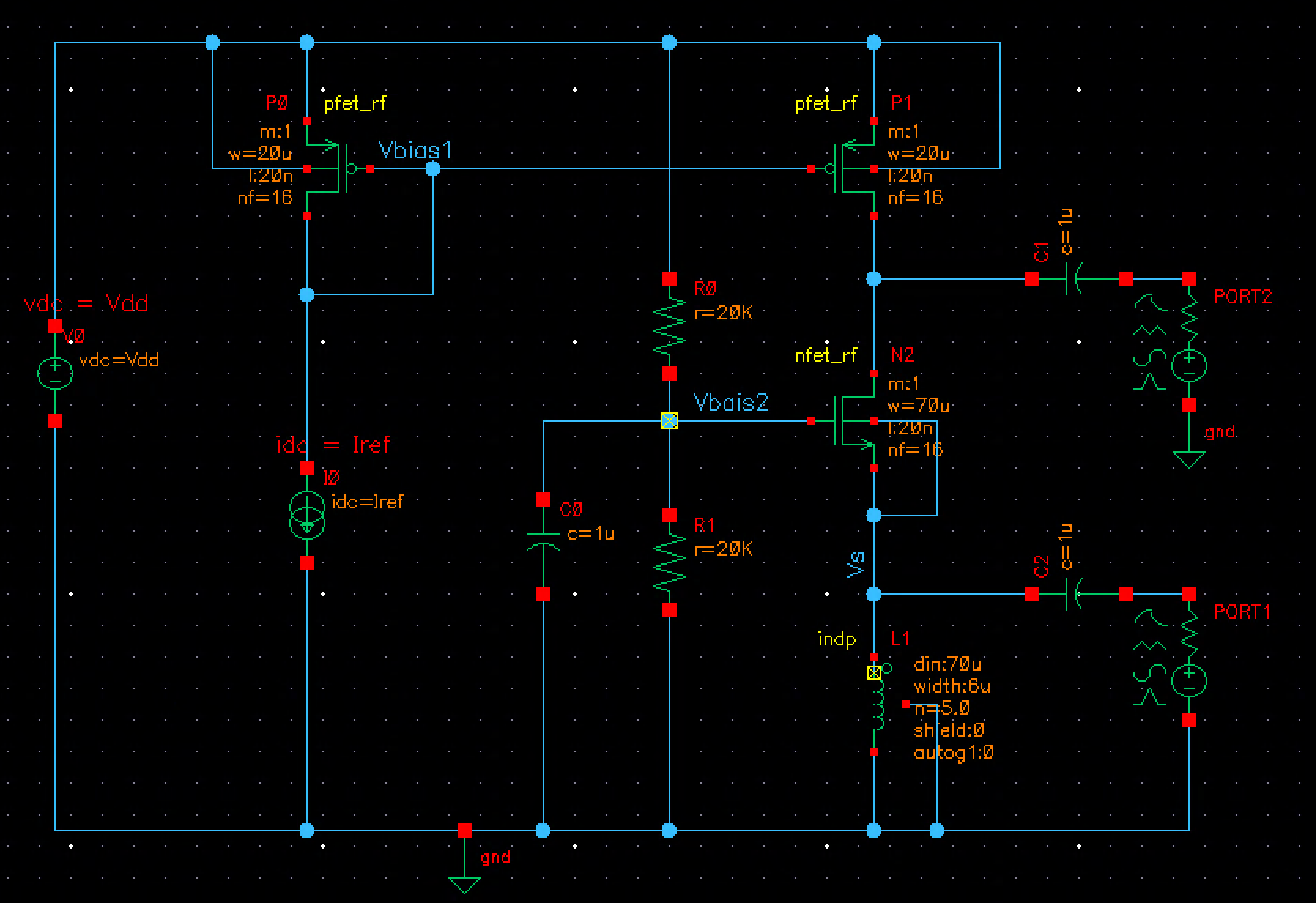

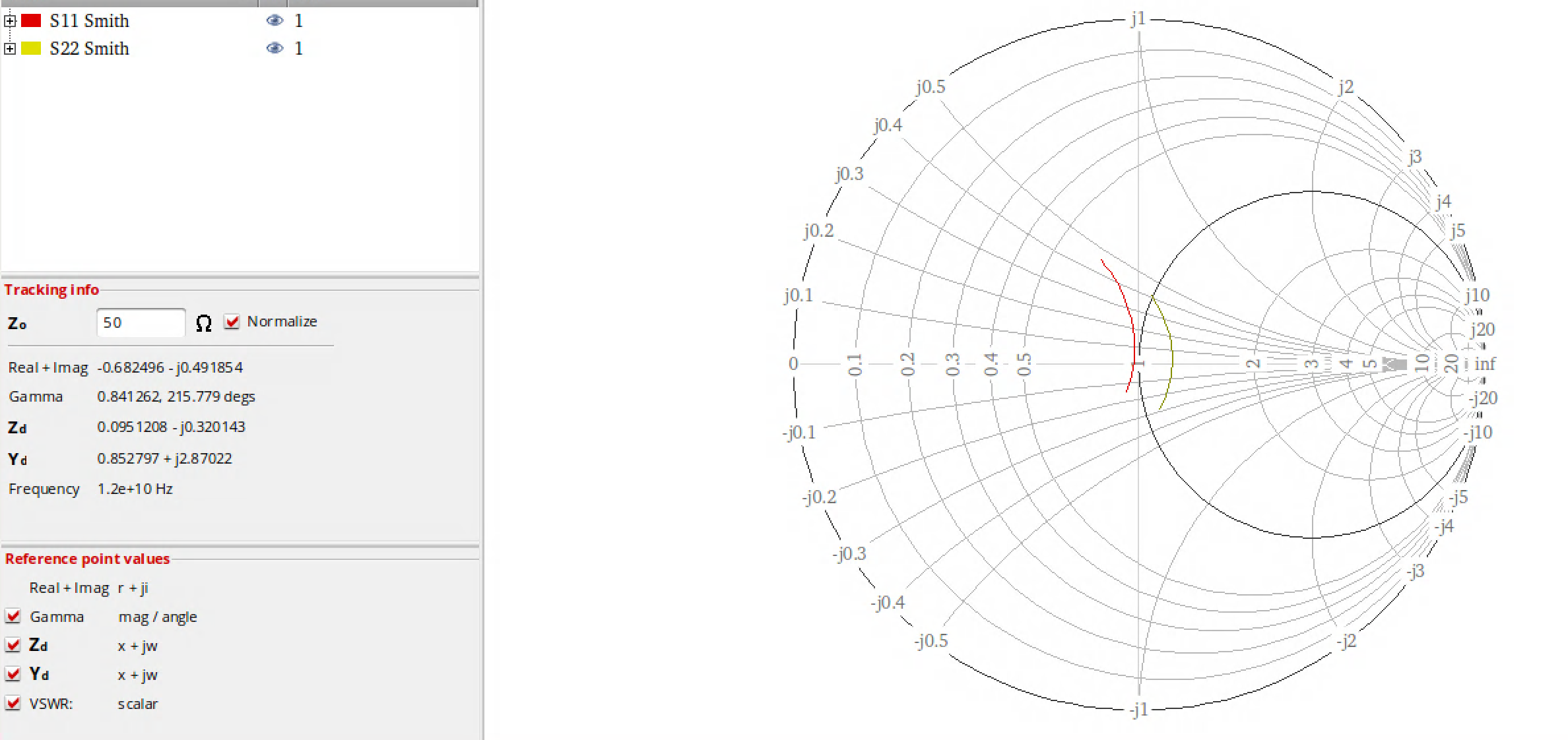

I tried it with the resistors and get a very different response. Iref = 1.5m and Id in this case is 1.9mA The biggest difference is the output impedance, which I want to keep large.

Relatively new to CMOS design so I had a pretty basic question. I am working on a common gate input stage to a amplifier. Above is the circuit schematic for the stage. I am trying to use current mirrors to set the drain current. From what I have read so far, it seems common practice to bias the PMOS current source with a current mirror to create an active load. But no examples I have read showed how to bias the gate properly. Is it bad to use a current mirror as well for the common gate biasing, or should I just use a resistive divider from Vdd? I got pretty good small signal results using this method. Id in this case was very close to Iref, as expected

I tried it with the resistors and get a very different response. Iref = 1.5m and Id in this case is 1.9mA The biggest difference is the output impedance, which I want to keep large.

Last edited: