I14R10

Full Member level 3

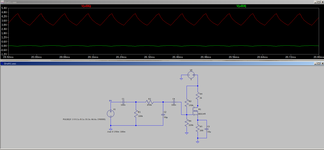

First of all, I will say I only have basics of analog electronics, so my design is probably wrong in so many places.

What I'm trying to do:

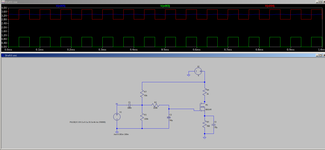

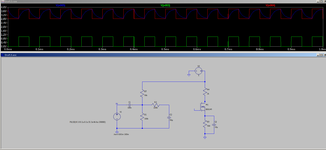

I have a square wave, but not from -V to +V, instead from 0 to V.

Next step, C1, R1 remove DC component of the signal

R2, C2 make low pass filter that gets me a triangle wave.

At this point, without the rest of the circuit to the right, I have an amplitude of around -0.4V to +0.4V at the junction of R2 and C2.

Now I want to amplify that signal with a MOSFET. MOSFET alone doesn't change my signal, but when I bias it to get a half of 5V on drain, those resistors for biasing lower the signal on the junction of R2, C2 and C4. What can I do to completely separate those two circuits so that I can bias MOSFET properly?

If I put an opamp as a buffer, things work. But let's say I don't want to use op Amps, how would I do it?

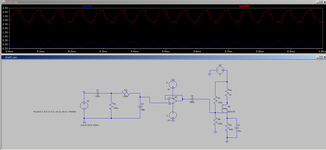

What I'm trying to do:

I have a square wave, but not from -V to +V, instead from 0 to V.

Next step, C1, R1 remove DC component of the signal

R2, C2 make low pass filter that gets me a triangle wave.

At this point, without the rest of the circuit to the right, I have an amplitude of around -0.4V to +0.4V at the junction of R2 and C2.

Now I want to amplify that signal with a MOSFET. MOSFET alone doesn't change my signal, but when I bias it to get a half of 5V on drain, those resistors for biasing lower the signal on the junction of R2, C2 and C4. What can I do to completely separate those two circuits so that I can bias MOSFET properly?

--- Updated ---

If I put an opamp as a buffer, things work. But let's say I don't want to use op Amps, how would I do it?

Attachments

Last edited: