elecfan

Member level 1

best practice for redundant microcontrollers!

Dear All

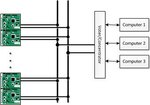

I am going to use two ARM micros in a redundant configuration, in which the slave micro comes to service, when the Master one fails to operate, or fails to provide an output.

since the operation needs to use the processing history, I have to keep both micros in active mode (Hot redundancy)

could u please share your experience, in what config I should design my system in order to improve the reliability of the system and also increase the life time of the slave mico?

Best regards

Dear All

I am going to use two ARM micros in a redundant configuration, in which the slave micro comes to service, when the Master one fails to operate, or fails to provide an output.

since the operation needs to use the processing history, I have to keep both micros in active mode (Hot redundancy)

could u please share your experience, in what config I should design my system in order to improve the reliability of the system and also increase the life time of the slave mico?

Best regards