stephane2788

Newbie

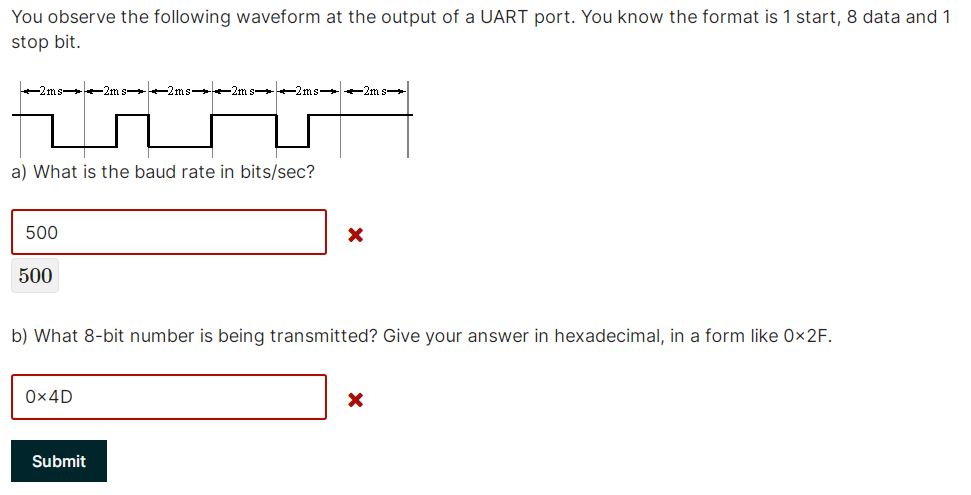

Hello, i'm doing a course on edX regarding UART and I have the below questions:

Can anybody help me understand why my values are wrong?

Can anybody help me understand why my values are wrong?