Sunshine_accu

Newbie

To all professionals,

I am new to FPGA design and have tried all my best to solve the error, but it still turned to be a failure. Therefore, I post to obtain some guidance, hopefully.

In detail, I instantiate module wgn_noise for two times and obtain two output signals—wgn_noise_I and wgn_noise_Q(all 9 bits).

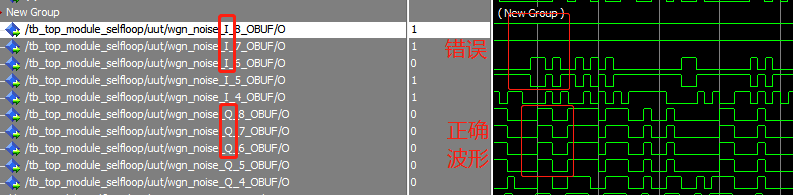

Strange is that the highest four bits of signal wgn_noise_Q are CORRECT. But the highest two bits of signal wgn_noise_I are always '1', and bit6 and bit5 are always opposite.The exact error are in the following screenshot.

The function of the module is to add AWGN nosie to input signal and is a tiny part of the whole project. In addition, the whole project works at 160M frequency and the timing is meeting requirement(No timin errors are reported).

I am new to FPGA design and have tried all my best to solve the error, but it still turned to be a failure. Therefore, I post to obtain some guidance, hopefully.

In detail, I instantiate module wgn_noise for two times and obtain two output signals—wgn_noise_I and wgn_noise_Q(all 9 bits).

Strange is that the highest four bits of signal wgn_noise_Q are CORRECT. But the highest two bits of signal wgn_noise_I are always '1', and bit6 and bit5 are always opposite.The exact error are in the following screenshot.

The function of the module is to add AWGN nosie to input signal and is a tiny part of the whole project. In addition, the whole project works at 160M frequency and the timing is meeting requirement(No timin errors are reported).