qwe221133

Newbie

Hi,

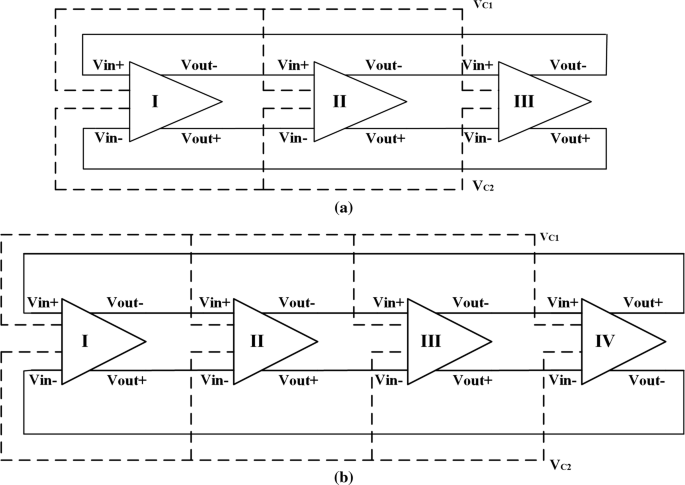

i need to design a CDR so i want to design a 4-stage ring oscillator for my phase detector,my stage schematic is in the picture below, i use hspice to simulate this VCO,i found that when i use 3-stage , VCO works,but in 4-stage it can't be oscillate,it's so weird!! I am pretty sure the circuit connected correctly, does anybody know the reason why 4-stage VCO can't oscillate?

i need to design a CDR so i want to design a 4-stage ring oscillator for my phase detector,my stage schematic is in the picture below, i use hspice to simulate this VCO,i found that when i use 3-stage , VCO works,but in 4-stage it can't be oscillate,it's so weird!! I am pretty sure the circuit connected correctly, does anybody know the reason why 4-stage VCO can't oscillate?