Mahruz

Junior Member level 3

Hi All,

I am kind of new to RF power amplifier design and I wanted to try and design a 800MHz RF power amplifier by myself using Microwave Office AWR .

I am trying to understand the design process involved in designing this 800MHz Power Amplifier.

From online books and videos, I understand the process to be as follows:

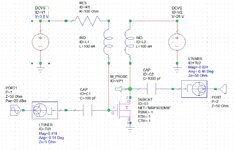

1. Obtain the transistor model. I am using NXP ( https://www.nxp.com/products/radio-...ideband-rf-power-ldmos-transistor:AFT09MS015N )

2. Chose a bias point. I wanted the PA to be a class A amplifier.

3. Perform stability analysis. Improve stability if rollet's factor is less than 1.

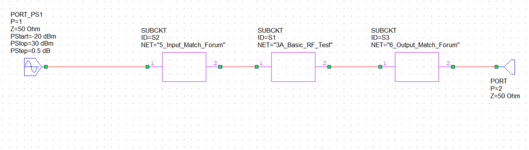

4. Design input and output matching networks against 50 Ohms.

5. Start with layout.( I have not reached layout part).

My questions are:

> Is the above process the correct process or did I miss out on any steps that can cause the PA not to function?

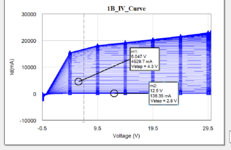

> How can I plot the loadline in AWR?

> Is there any example in AWR that a beginner can use to understand and replicate for a PA design?

Thank you for sharing your knowledge.

I am kind of new to RF power amplifier design and I wanted to try and design a 800MHz RF power amplifier by myself using Microwave Office AWR .

I am trying to understand the design process involved in designing this 800MHz Power Amplifier.

From online books and videos, I understand the process to be as follows:

1. Obtain the transistor model. I am using NXP ( https://www.nxp.com/products/radio-...ideband-rf-power-ldmos-transistor:AFT09MS015N )

2. Chose a bias point. I wanted the PA to be a class A amplifier.

3. Perform stability analysis. Improve stability if rollet's factor is less than 1.

4. Design input and output matching networks against 50 Ohms.

5. Start with layout.( I have not reached layout part).

My questions are:

> Is the above process the correct process or did I miss out on any steps that can cause the PA not to function?

> How can I plot the loadline in AWR?

> Is there any example in AWR that a beginner can use to understand and replicate for a PA design?

Thank you for sharing your knowledge.