VictorWu

Newbie level 5

Hello everyone,

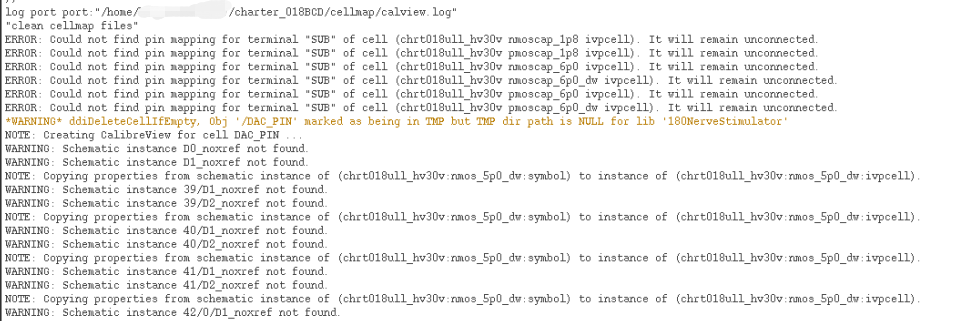

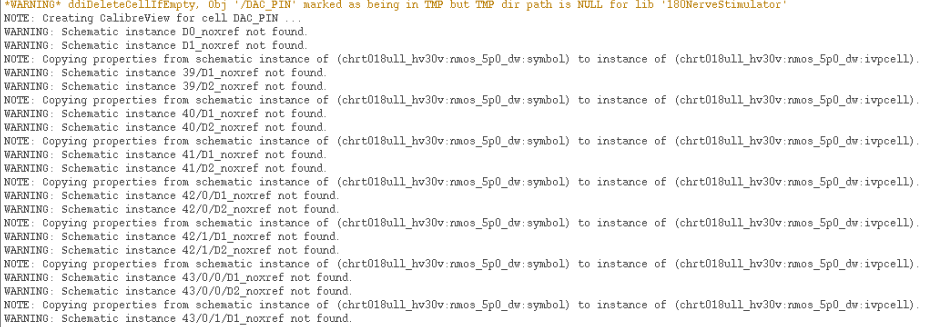

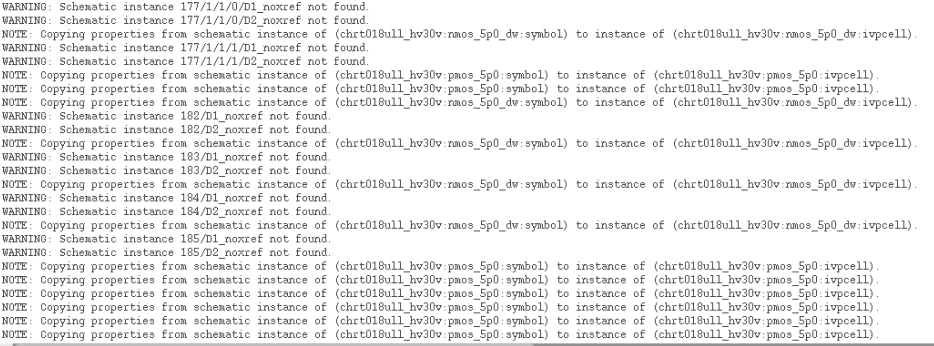

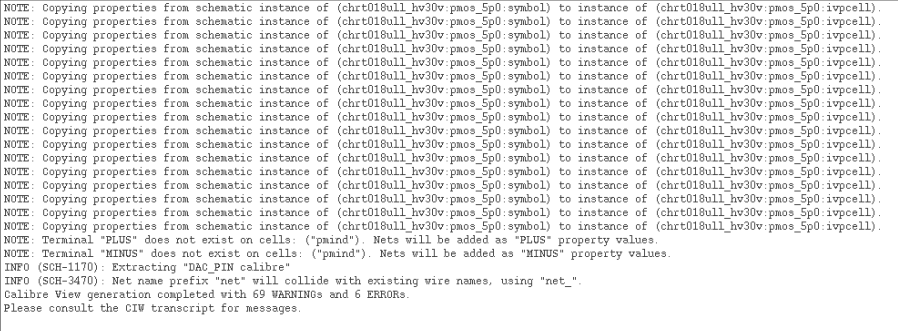

I'm using Charter_018BCD PDK. I made a DAC and have performed DRC, LVS successfully. But when I performed PEX whose output is CalView, I ran into some problems. The error show as follows:

"error: Could not find pin mapping for terminal "SUB" of cell (chart018ull_hv30v nmoscap_1p8 ivpcell). It will remain unconnected."

"error: Could not find pin mapping for terminal "SUB" of cell (chart018ull_hv30v pmoscap_1p8 ivpcell). It will remain unconnected."

"error: Could not find pin mapping for terminal "SUB" of cell (chart018ull_hv30v nmoscap_6p0 ivpcell). It will remain unconnected."

"error: Could not find pin mapping for terminal "SUB" of cell (chart018ull_hv30v nmoscap_6p0_dw ivpcell). It will remain unconnected."

"error: Could not find pin mapping for terminal "SUB" of cell (chart018ull_hv30v pmoscap_6p0 ivpcell). It will remain unconnected."

"error: Could not find pin mapping for terminal "SUB" of cell (chart018ull_hv30v pmoscap_6p0_dw ivpcell). It will remain unconnected."

I don't understand what these errors mean, and what should I do to eliminate these errors.In my circut, there is no pin "SUB". I will attach some screenshots of errors and warnings.

Dose anyone kown how to solve these problems?

Thanks!

I'm using Charter_018BCD PDK. I made a DAC and have performed DRC, LVS successfully. But when I performed PEX whose output is CalView, I ran into some problems. The error show as follows:

"error: Could not find pin mapping for terminal "SUB" of cell (chart018ull_hv30v nmoscap_1p8 ivpcell). It will remain unconnected."

"error: Could not find pin mapping for terminal "SUB" of cell (chart018ull_hv30v pmoscap_1p8 ivpcell). It will remain unconnected."

"error: Could not find pin mapping for terminal "SUB" of cell (chart018ull_hv30v nmoscap_6p0 ivpcell). It will remain unconnected."

"error: Could not find pin mapping for terminal "SUB" of cell (chart018ull_hv30v nmoscap_6p0_dw ivpcell). It will remain unconnected."

"error: Could not find pin mapping for terminal "SUB" of cell (chart018ull_hv30v pmoscap_6p0 ivpcell). It will remain unconnected."

"error: Could not find pin mapping for terminal "SUB" of cell (chart018ull_hv30v pmoscap_6p0_dw ivpcell). It will remain unconnected."

I don't understand what these errors mean, and what should I do to eliminate these errors.In my circut, there is no pin "SUB". I will attach some screenshots of errors and warnings.

Dose anyone kown how to solve these problems?

Thanks!