franticEB

Full Member level 3

Hi,

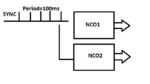

i've to generate 2 sinusoidal signal (70Hz) in phase.

The problem is that those signals are generated by 2 altera nco on different fpga.

There is a 10Hz sync signal available

Thanks

How could i use that sync signal in order to put in phase two sinusoid or to correct the phase during normal operation?

Could you help me

i've to generate 2 sinusoidal signal (70Hz) in phase.

The problem is that those signals are generated by 2 altera nco on different fpga.

There is a 10Hz sync signal available

Thanks

How could i use that sync signal in order to put in phase two sinusoid or to correct the phase during normal operation?

Could you help me