ljp2706

Advanced Member level 4

Hello,

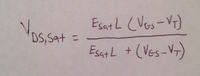

I am working in a sub 1 volt supply at the 14nm node. I have created an amplifier for a bandgap voltage reference. My issue that I was wondering if someone might be able to point me in the right direction lies with the differential input pair. When I run monte carlo, there are two points in which the VDS of the differential input falls below saturation for cold temperatures. I have tried to use helper transistors to keep the differential input in saturation, but it isn't working very well, are there any other methods I can attempt to implement to ensure the input remains saturated for all monte carlo points?

Thanks!

I am working in a sub 1 volt supply at the 14nm node. I have created an amplifier for a bandgap voltage reference. My issue that I was wondering if someone might be able to point me in the right direction lies with the differential input pair. When I run monte carlo, there are two points in which the VDS of the differential input falls below saturation for cold temperatures. I have tried to use helper transistors to keep the differential input in saturation, but it isn't working very well, are there any other methods I can attempt to implement to ensure the input remains saturated for all monte carlo points?

Thanks!