Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

That won't work

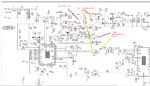

Makes no sense for the post #1 schematic which has the switching node shorted to COM.And the voltage I am seeing 760V is (Com referenced to ground)

It shows just a basic flyback converter. So we are still left in the dark about the actual "active clamping circuit".Sure the schematic have is based on this

capacitor too small respectively leakage inductance too high

There are problems with the clamp cap getting too high faradic value...basso discusses these in his book "switch mode power supplies"...towards the latter part of the book.I changed the value I had of 1.5nF to the same as they have at 10nF and it dropped to 720V, if i go too high of value i take it there will not be enough time to discharge the capacitor completely?

basso discusses these in his book "switch mode power supplies"...towards the latter part of the book.

.In an Active Clamp Forward converter, it is also possible to arrange it to get ZVS of the FET, but again, rarely is it actually worth doing this, and you just use the active clamp for the fact that it resets the leakage inductance in a forward converter without necessarily needing a high side FET.

In the active clamp forward converter, you have a “reset FET”, which you switch on at certain times in each switching cycle, so as to let the leakage inductor’s current “go back the other way”, …then when you’ve got it ‘going back the other way’, you cunningly switch the ‘reset FET’ off, and then the leakage inductor current is forced to flow in a path that ends up discharging the cds capacitance of the main power fet…then when the Vds of this fet is zero, you switch it on.

So that is it in brief, in resonant converters you get an inductive current flowing, and of course, as you know, you cannot break an inductive current, so , just before you switch on the relevant fet (the one in which you wish to achieve ZVS), you re-direct the inductive current, (perhaps by switching off a fet in which it is flowing) and the inductive current then re-directs and then discharges the Cds capacitance of the fet that you are just about to switch on…..to the point where the switch-on happens when its Vds is zero….that is in brief how resonant converters often operate

- clamp control isn't working correctly (capacitor isn't discharged during off-time)