T

treez

Guest

Hello,

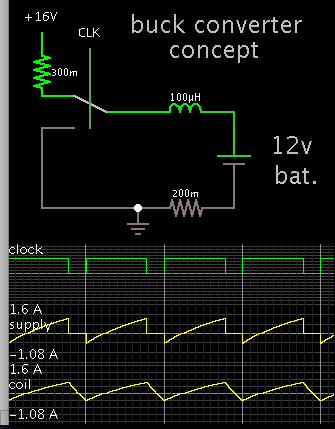

Have you ever seen a sync buck controller that does not have the facility to detect overly high reverse current flow in the synchronous FET?

Have you ever seen a sync buck controller that does not have the facility to detect overly high reverse current flow in the synchronous FET?