preethi19

Full Member level 5

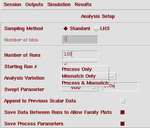

Hi can anyone pls tell me the difference between process analysis and mismatch analysis. I thought both were same. Nothing but varying the transistor dimensions to see during fabrication process if some errors causing slight change in dimensions of the transistors are caused, how well the circuit behaves. But then in monte carlo analysis-> in analysis variation why do we have process only, mismatch only and process and mismatch. Can someone pls tell whats the actual difference.

When simulation is run transistor dimensions are varied but say how can i determine in wat range is it varying. Suppose a transistor is 1u/1u (W/L).. Then how can i find out what is varied and of how much value. Becoz i think there is some tolerance right. Meaning we can choose right that variation is 5% or 10%. How can i do and find all that in cadence?

Finally i am looking to plot this graph for a 4Q multiplier.

Like i just give 100 runs in monte carlo and i do get a DC analysis output wer i can see the output varying from one another. But i still cant select each transistor and check how much it is varied and don't understand how to plot it as the above graph. Since i need a histogram in

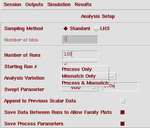

Results->Plot-> Histogram i get the following

Can anyone pls explain me what is this par 1, par 2 etc. Becoz all seem to give a histogram but i am not sure which one is the right one to plot THD percent. I am not able to determine the X axis if its percent or what. Its just like X(). Would be really great if somebody could help!!!

When simulation is run transistor dimensions are varied but say how can i determine in wat range is it varying. Suppose a transistor is 1u/1u (W/L).. Then how can i find out what is varied and of how much value. Becoz i think there is some tolerance right. Meaning we can choose right that variation is 5% or 10%. How can i do and find all that in cadence?

Finally i am looking to plot this graph for a 4Q multiplier.

Like i just give 100 runs in monte carlo and i do get a DC analysis output wer i can see the output varying from one another. But i still cant select each transistor and check how much it is varied and don't understand how to plot it as the above graph. Since i need a histogram in

Results->Plot-> Histogram i get the following

Can anyone pls explain me what is this par 1, par 2 etc. Becoz all seem to give a histogram but i am not sure which one is the right one to plot THD percent. I am not able to determine the X axis if its percent or what. Its just like X(). Would be really great if somebody could help!!!