Alper özel

Member level 1

- Joined

- Feb 28, 2015

- Messages

- 40

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 6

- Location

- Turkey / Scotland

- Activity points

- 487

I have to use LtSpice to design an opAmp with pre determined MOS library: http://ptm.asu.edu/modelcard/2006/130nm_bulk.pm

However, I have no experience with LtSpice before and I really could not find what I want on internet so I am asking to you: How do I calculate the Vth so Mn*Cox in LtSpice?

I thought Vth0=0.378 was the threshold value of NMOS and Vth=-0.321 of PMOS according to the library text:

+vth0 = 0.3782 k1 = 0.4 k2 = 0.01 k3 = 0

+vth0 = -0.321 k1 = 0.4 k2 = -0.01 k3 = 0

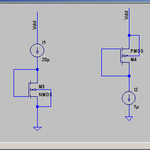

However when I calculate the NMOS MnCox for I=10 u and 20 u in this configuration:

I get MnCox as 1.32m and 0.9m differently. So this calculation makes no sense. And what is the correct way to calculate it? Thanks.

However, I have no experience with LtSpice before and I really could not find what I want on internet so I am asking to you: How do I calculate the Vth so Mn*Cox in LtSpice?

I thought Vth0=0.378 was the threshold value of NMOS and Vth=-0.321 of PMOS according to the library text:

+vth0 = 0.3782 k1 = 0.4 k2 = 0.01 k3 = 0

+vth0 = -0.321 k1 = 0.4 k2 = -0.01 k3 = 0

However when I calculate the NMOS MnCox for I=10 u and 20 u in this configuration:

I get MnCox as 1.32m and 0.9m differently. So this calculation makes no sense. And what is the correct way to calculate it? Thanks.